24531904_j

24531904_j 24531904_j

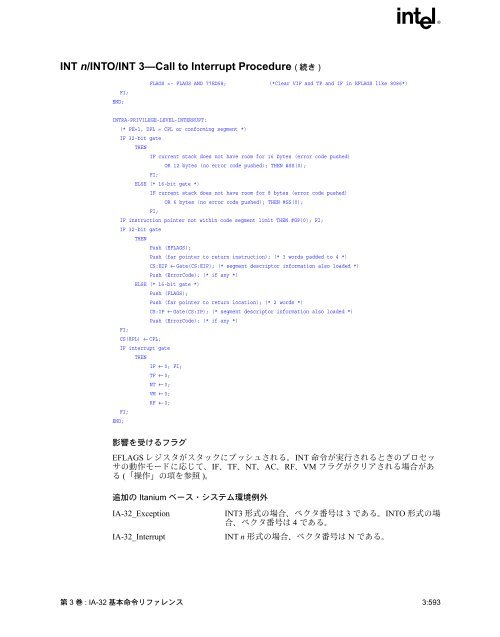

INT n/INTO/INT 3—Call to Interrupt Procedure ( 続き ) END; VM86_INTERRUPT_TO_PRIV0: tempEFLAGS ← EFLAGS; VM ← 0; TF ← 0; RF ← 0; IF service through interrupt gate THEN IF ← 0; FI; TempSS ← SS; TempESP ← ESP; SS:ESP ← TSS(SS0:ESP0); (* Change to level 0 stack segment *) (* Following pushes are 16 bits for 16-bit gate and 32 bits for 32-bit gates *) (* Segment selector pushes in 32-bit mode are padded to two words *) Push(GS); Push(FS); Push(DS); Push(ES); Push(TempSS); Push(TempESP); Push(TempEFlags); Push(CS); Push(EIP); GS ← 0; (*segment registers nullified, invalid in protected mode *) FS ← 0; DS ← 0; ES ← 0; CS ← Gate(CS); IF OperandSize=32 THEN EIP ← Gate(instruction pointer); ELSE (* OperandSize is 16 *) EIP ← Gate(instruction pointer) AND 0000FFFFH; FI; (* Starts execution of new routine in Protected Mode *) END; VM86_INTERRUPT_TO_VM86: IF IOPL = 3 THEN push(FLAGS OR 3000H); (*Push FLAGS w/ IOPL bits as 11B or IOPL 3*) push(CS); push(IP); CS

INT n/INTO/INT 3—Call to Interrupt Procedure ( 続き ) FI; END; FLAGS

- Seite 554 und 555: FSTCW/FNSTCW—Store Control Word (

- Seite 556 und 557: FSTENV/FNSTENV—Store FPU Environm

- Seite 558 und 559: FSTSW/FNSTSW—Store Status Word (

- Seite 560 und 561: FSUB/FSUBP/FISUB—Subtract ( 続

- Seite 562 und 563: FSUBR/FSUBRP/FISUBR—Reverse Subtr

- Seite 564 und 565: FSUBR/FSUBRP/FISUBR—Reverse Subtr

- Seite 566 und 567: FTST—TEST オペコード 命令

- Seite 568 und 569: FUCOM/FUCOMP/FUCOMPP—Unordered Co

- Seite 570 und 571: FWAIT—Wait 本章の 「WAIT」

- Seite 572 und 573: FXAM—Examine ( 続き ) 実アド

- Seite 574 und 575: FXCH—Exchange Register Contents (

- Seite 576 und 577: FXTRACT—Extract Exponent and Sign

- Seite 578 und 579: FYL2X—Compute y ∗ log 2 x ( 続

- Seite 580 und 581: FYL2XP1—Compute y ∗ log 2 (x +1

- Seite 582 und 583: IDIV—Signed Divide オペコー

- Seite 584 und 585: IDIV—Signed Divide ( 続き ) 実

- Seite 586 und 587: IMUL—Signed Multiply ( 続き ) 2

- Seite 588 und 589: IMUL—Signed Multiply ( 続き )

- Seite 590 und 591: IN—Input from Port ( 続き ) 操

- Seite 592 und 593: INC—Increment by 1 オペコー

- Seite 594 und 595: INS/INSB/INSW/INSD—Input from Por

- Seite 596 und 597: INS/INSB/INSW/INSD—Input from Por

- Seite 598 und 599: INT n/INTO/INT 3—Call to Interrup

- Seite 600 und 601: INT n/INTO/INT 3—Call to Interrup

- Seite 602 und 603: INT n/INTO/INT 3—Call to Interrup

- Seite 606 und 607: INT n/INTO/INT 3—Call to Interrup

- Seite 608 und 609: INT n/INTO/INT 3—Call to Interrup

- Seite 610 und 611: INVD—Invalidate Internal Caches (

- Seite 612 und 613: IRET/IRETD—Interrupt Return オ

- Seite 614 und 615: IRET/IRETD—Interrupt Return ( 続

- Seite 616 und 617: IRET/IRETD—Interrupt Return ( 続

- Seite 618 und 619: IRET/IRETD—Interrupt Return ( 続

- Seite 620 und 621: Jcc—Jump if Condition Is Met オ

- Seite 622 und 623: Jcc—Jump if Condition Is Met (

- Seite 624 und 625: JMP—Jump オペコード 命令

- Seite 626 und 627: JMP—Jump ( 続き ) 操作 IF nea

- Seite 628 und 629: JMP—Jump ( 続き ) END; TASK-GAT

- Seite 630 und 631: JMP—Jump ( 続き ) #PF ( フォ

- Seite 632 und 633: JMPE—Jump to Intel ® Itanium ®

- Seite 634 und 635: LAR—Load Access Rights Byte オ

- Seite 636 und 637: LAR—Load Access Rights Byte ( 続

- Seite 638 und 639: LDS/LES/LFS/LGS/LSS—Load Far Poin

- Seite 640 und 641: LEA—Load Effective Address オペ

- Seite 642 und 643: LEAVE—High Level Procedure Exit

- Seite 644 und 645: LES—Load Full Pointer 「LDS/LES/

- Seite 646 und 647: LGDT/LIDT—Load Global/Interrupt D

- Seite 648 und 649: LGS—Load Full Pointer 「LDS/LES/

- Seite 650 und 651: LLDT—Load Local Descriptor Table

- Seite 652 und 653: LMSW—Load Machine Status Word オ

INT n/INTO/INT 3—Call to Interrupt Procedure ( 続き )<br />

FI;<br />

END;<br />

FLAGS