24531904_j

24531904_j 24531904_j

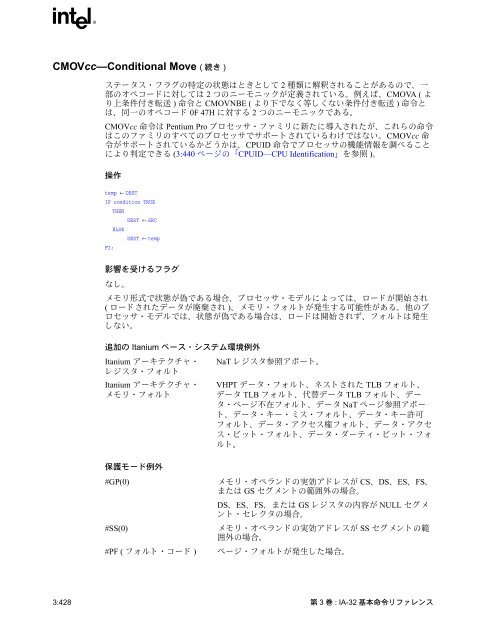

CMOVcc—Conditional Move ( 続き ) ス テ ー タ ス ・ フ ラ グの特定の状態は と き と して 2 種類に解釈される こ と があるので、 一 部のオペコ ー ド に対しては 2 つのニーモニ ッ クが定義されている。 例えば、 CMOVA ( よ り上条件付き転送) 命令 と CMOVNBE ( よ り 下でな く 等し く ない条件付き転送 ) 命令 と は、 同一のオペコ ー ド 0F 47H に対する 2 つのニーモニッ クである。 CMOVcc 命令は Pentium Pro プ ロ セ ッ サ ・ フ ァ ミ リ に新たに導入 さ れたが、 こ れ ら の命令 はこのファミ リのすべてのプロセッサでサポート されているわけではない。 CMOVcc 命 令がサポ ー ト されているかど う かは、 CPUID 命令でプ ロ セ ッ サの機能情報を調べ る こ と により判定できる (3:440 ページの 「CPUID—CPU Identification」 を参照 )。 操作 temp ← DEST IF condition TRUE THEN DEST ← SRC ELSE DEST ← temp FI; 影響を受けるフラグ なし。 メ モ リ 形式で状態が偽であ る場合、 プ ロ セ ッ サ ・ モデルに よ っ ては、 ロ ー ド が開始 さ れ ( ロード されたデータが廃棄され)、 メモリ ・ フォル トが発生する可能性がある。 他のプ ロ セ ッ サ ・ モデルでは、 状態が偽である場合は、 ロ ー ド は開始 さ れず、 フ ォ ル ト は発生 しない。 追加の Itanium ベース・システム環境例外 Itanium アーキテクチャ ・ レジスタ ・ フォルト Itanium アーキテクチャ ・ メモリ ・ フォル ト NaT レ ジ ス タ参照アボ ー ト 。 VHPT データ ・ フォル ト、 ネス ト された TLB フォルト、 データ TLB フォルト、 代替データTLB フォルト、 デー タ・ページ不在フォルト、 データNaT ページ参照アボー ト、 データ・キー・ ミス・フォルト、 データ・キー許可 フォルト、 データ・アクセス権フォルト、 データ・アクセ ス・ビット ・フォルト、 データ・ダーティ ・ビット ・フォ ルト。 保護モード例外 #GP(0) メモリ ・ オペランドの実効アドレスが CS、 DS、 ES、 FS、 または GS セグ メ ン ト の範囲外の場合。 DS、 ES、 FS、 または GS レジスタの内容がNULL セグメ ン ト ・ セ レ ク タ の場合。 #SS(0) メモリ ・ オペランドの実効アドレスが SS セグメン ト の範 囲外の場合。 #PF ( フォルト ・コード ) ペー ジ ・ フ ォ ル ト が発生した場合。 3:428 第 3 巻 : IA-32 基本命令リファレンス

CMOVcc—Conditional Move ( 続き ) #AC(0) 現行特権レベルが 3 のときに、 アライメント ・チェックが イネーブルにされていて、 アライメントが合わないメモリ 参照が行われた場合。 実アドレス・モード例外 #GP メモリ ・ オペランドの実効アドレスが CS、 DS、 ES、 FS、 または GS セグ メ ン ト の範囲外の場合。 #SS メモリ ・ オペランドの実効アドレスが SS セグメン ト の範 囲外の場合。 仮想 8086 モード例外 #GP(0) メモリ ・ オペランドの実効アドレスが CS、 DS、 ES、 FS、 または GS セグ メ ン ト の範囲外の場合。 #SS(0) メモリ ・ オペランドの実効アドレスが SS セグメン ト の範 囲外の場合。 #PF ( フォルト ・コード ) ペー ジ ・ フ ォ ル ト が発生した場合。 #AC(0) アライメン ト ・ チェ ッ クがイネーブルにされていて、 アラ イ メン ト が合わないメモ リ 参照が行われた場合。 第 3 巻 : IA-32 基本命令リファレンス 3:429

- Seite 390 und 391: 図 1-1. BIT[EAX,21] のビット

- Seite 392 und 393: 1.2.7 仮想 8086 モード例外

- Seite 394 und 395: AAD ─ ASCII Adjust AX Before Divi

- Seite 396 und 397: AAS ─ ASCII Adjust AL After Subtr

- Seite 398 und 399: ADC ─ Add with Carry ( 続き )

- Seite 400 und 401: ADD ─ Add ( 続き ) 保護モー

- Seite 402 und 403: AND ─ Logical AND ( 続き ) 保

- Seite 404 und 405: ARPL ─ Adjust RPL Field of Segmen

- Seite 406 und 407: BOUND ─ Check Array Index Against

- Seite 408 und 409: BSF ─ Bit Scan Forward ( 続き )

- Seite 410 und 411: BSR ─ Bit Scan Reverse ( 続き )

- Seite 412 und 413: BT ─ Bit Test オペコード 命

- Seite 414 und 415: BTC ─ Bit Test and Complement オ

- Seite 416 und 417: BTR ─ Bit Test and Reset オペ

- Seite 418 und 419: BTS ─ Bit Test and Set オペコ

- Seite 420 und 421: CALL ─ Call Procedure オペコ

- Seite 422 und 423: CALL ─ Call Procedure ( 続き )

- Seite 424 und 425: CALL ─ Call Procedure ( 続き )

- Seite 426 und 427: CALL ─ Call Procedure ( 続き )

- Seite 428 und 429: CALL ─ Call Procedure ( 続き )

- Seite 430 und 431: CBW/CWDE ─ Convert Byte to Word/C

- Seite 432 und 433: CLC ─ Clear Carry Flag オペコ

- Seite 434 und 435: CLI ─ Clear Interrupt Flag オペ

- Seite 436 und 437: CLTS—Clear Task-Switched Flag in

- Seite 438 und 439: CMOVcc—Conditional Move オペコ

- Seite 442 und 443: CMP—Compare Two Operands オペ

- Seite 444 und 445: CMPS/CMPSB/CMPSW/CMPSD—Compare St

- Seite 446 und 447: CMPS/CMPSB/CMPSW/CMPSD—Compare St

- Seite 448 und 449: CMPXCHG—Compare and Exchange (

- Seite 450 und 451: CMPXCHG8B—Compare and Exchange 8

- Seite 452 und 453: CPUID—CPU Identification オペ

- Seite 454 und 455: CPUID—CPU Identification ( 続き

- Seite 456 und 457: CPUID—CPU Identification ( 続き

- Seite 458 und 459: CWDE—Convert Word to Doubleword

- Seite 460 und 461: DAS—Decimal Adjust AL after Subtr

- Seite 462 und 463: DEC—Decrement by 1 ( 続き ) #AC

- Seite 464 und 465: DIV—Unsigned Divide ( 続き ) FI

- Seite 466 und 467: ENTER—Make Stack Frame for Proced

- Seite 468 und 469: ENTER—Make Stack Frame for Proced

- Seite 470 und 471: F2XM1—Compute 2 x -1 ( 続き )

- Seite 472 und 473: FADD/FADDP/FIADD—Add オペコー

- Seite 474 und 475: FADD/FADDP/FIADD—Add ( 続き )

- Seite 476 und 477: FBLD—Load Binary Coded Decimal

- Seite 478 und 479: FBSTP—Store BCD Integer and Pop

- Seite 480 und 481: FBSTP—Store BCD Integer and Pop (

- Seite 482 und 483: FCLEX/FNCLEX—Clear Exceptions オ

- Seite 484 und 485: FCMOVcc—Floating-Point Conditiona

- Seite 486 und 487: FCOM/FCOMP/FCOMPP—Compare Real (

- Seite 488 und 489: FCOMI/FCOMIP/FUCOMI/FUCOMIP—Compa

CMOVcc—Conditional Move ( 続き )<br />

ス テ ー タ ス ・ フ ラ グの特定の状態は と き と して 2 種類に解釈される こ と があるので、 一<br />

部のオペコ ー ド に対しては 2 つのニーモニ ッ クが定義されている。 例えば、 CMOVA ( よ<br />

り上条件付き転送) 命令 と CMOVNBE ( よ り 下でな く 等し く ない条件付き転送 ) 命令 と<br />

は、 同一のオペコ ー ド 0F 47H に対する 2 つのニーモニッ クである。<br />

CMOVcc 命令は Pentium Pro プ ロ セ ッ サ ・ フ ァ ミ リ に新たに導入 さ れたが、 こ れ ら の命令<br />

はこのファミ リのすべてのプロセッサでサポート されているわけではない。 CMOVcc 命<br />

令がサポ ー ト されているかど う かは、 CPUID 命令でプ ロ セ ッ サの機能情報を調べ る こ と<br />

により判定できる (3:440 ページの 「CPUID—CPU Identification」 を参照 )。<br />

操作<br />

temp ← DEST<br />

IF condition TRUE<br />

THEN<br />

DEST ← SRC<br />

ELSE<br />

DEST ← temp<br />

FI;<br />

影響を受けるフラグ<br />

なし。<br />

メ モ リ 形式で状態が偽であ る場合、 プ ロ セ ッ サ ・ モデルに よ っ ては、 ロ ー ド が開始 さ れ<br />

( ロード されたデータが廃棄され)、 メモリ ・ フォル トが発生する可能性がある。 他のプ<br />

ロ セ ッ サ ・ モデルでは、 状態が偽である場合は、 ロ ー ド は開始 さ れず、 フ ォ ル ト は発生<br />

しない。<br />

追加の Itanium ベース・システム環境例外<br />

Itanium アーキテクチャ ・<br />

レジスタ ・ フォルト<br />

Itanium アーキテクチャ ・<br />

メモリ ・ フォル ト<br />

NaT レ ジ ス タ参照アボ ー ト 。<br />

VHPT データ ・ フォル ト、 ネス ト された TLB フォルト、<br />

データ TLB フォルト、 代替データTLB フォルト、 デー<br />

タ・ページ不在フォルト、 データNaT ページ参照アボー<br />

ト、 データ・キー・ ミス・フォルト、 データ・キー許可<br />

フォルト、 データ・アクセス権フォルト、 データ・アクセ<br />

ス・ビット ・フォルト、 データ・ダーティ ・ビット ・フォ<br />

ルト。<br />

保護モード例外<br />

#GP(0) メモリ ・ オペランドの実効アドレスが CS、 DS、 ES、 FS、<br />

または GS セグ メ ン ト の範囲外の場合。<br />

DS、 ES、 FS、 または GS レジスタの内容がNULL セグメ<br />

ン ト ・ セ レ ク タ の場合。<br />

#SS(0) メモリ ・ オペランドの実効アドレスが SS セグメン ト の範<br />

囲外の場合。<br />

#PF ( フォルト ・コード ) ペー ジ ・ フ ォ ル ト が発生した場合。<br />

3:428 第 3 巻 : IA-32 基本命令リファレンス