Paralleladdierer und -subtrahierer Paralleladdierer und -subtrahierer

Paralleladdierer und -subtrahierer Paralleladdierer und -subtrahierer

Paralleladdierer und -subtrahierer Paralleladdierer und -subtrahierer

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

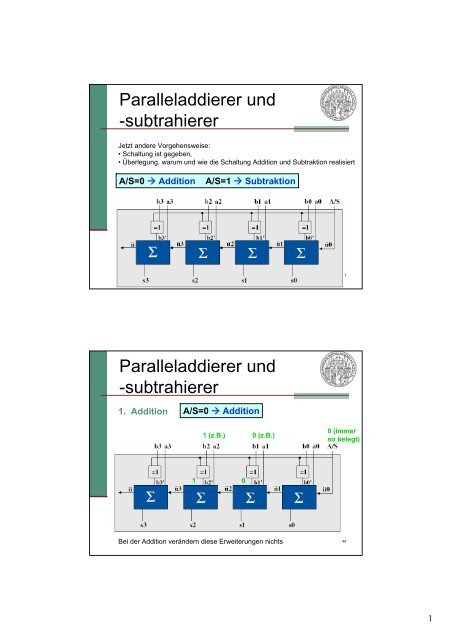

<strong>Paralleladdierer</strong> <strong>und</strong><br />

-<strong>subtrahierer</strong><br />

Jetzt andere Vorgehensweise:<br />

• Schaltung ist gegeben,<br />

• Überlegung, warum <strong>und</strong> wie die Schaltung Addition <strong>und</strong> Subtraktion realisiert<br />

A/S=0 � Addition A/S=1 � Subtraktion<br />

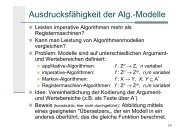

<strong>Paralleladdierer</strong> <strong>und</strong><br />

-<strong>subtrahierer</strong><br />

1. Addition<br />

A/S=0 � Addition<br />

1<br />

1 (z.B.) 0 (z.B.)<br />

Bei der Addition verändern diese Erweiterungen nichts<br />

0<br />

43<br />

0 (immer<br />

so belegt)<br />

44<br />

1

<strong>Paralleladdierer</strong> <strong>und</strong><br />

-<strong>subtrahierer</strong><br />

1. Subtraktion<br />

Bei der Subtraktion:<br />

• Invertierung aller Zeichen <strong>und</strong><br />

• Addition von 1<br />

0<br />

A/S=1 � Subtraktion<br />

1 (z.B.) 0 (z.B.)<br />

<strong>Paralleladdierer</strong> <strong>und</strong><br />

-<strong>subtrahierer</strong><br />

1<br />

A/S=0 � Addition<br />

A/S=1 � Subtraktion<br />

a 1..n ,<br />

b 1..n : Eingänge<br />

n+1 Ausgänge<br />

1 (immer<br />

so belegt)<br />

45<br />

46<br />

2

<strong>Paralleladdierer</strong> <strong>und</strong><br />

-<strong>subtrahierer</strong><br />

Beispiel: Addition von a=3 (0011) <strong>und</strong> b=2 (0010):<br />

<strong>Paralleladdierer</strong> <strong>und</strong><br />

-<strong>subtrahierer</strong><br />

Beispiel: Subtraktion von a=5 (0101) <strong>und</strong> b=3 (0011):<br />

47<br />

48<br />

3

<strong>Paralleladdierer</strong> <strong>und</strong> -<br />

<strong>subtrahierer</strong><br />

Beispiel: Subtraktion von a=2 (0010) <strong>und</strong> b=5 (0101):<br />

Carry-Select-Addiernetze<br />

Bisher war Addiernetz zur Addition zweier n-stelliger Dualzahlen<br />

nur mittels n Volladdierern realisierbar:<br />

� Sicherstellen, dass am u-Eingang des<br />

1. Volladdierers stets eine 0 anliegt.<br />

� als Carry-Ripple- oder Carry-Chain-Adder<br />

(Übertrags:, Übertrags:)<br />

bezeichnet, da endgültiger Übertrag (wie<br />

bei der schriftlichen Addition von rechts<br />

nach links) durch das Schaltnetz<br />

geschoben wird.<br />

Problem bei hoher Stellenanzahl � viele Schaltstufen<br />

� zeitaufwändig, bis Volladdierer nacheinander ihre<br />

Operationen ausgeführt haben<br />

49<br />

50<br />

4

Andere Variante: Carry-<br />

Save-Addiernetze<br />

1. In 1. Stufe � 3 Summanden stellenweise zu einer Summe<br />

zusammenaddiert, Überträge sind nicht in dieser Summe<br />

enthalten, werden eigens festgehalten<br />

2. In weiteren Stufen kommt zu der Summe <strong>und</strong> dem Übertrag<br />

immer je ein neuer Summand hinzu.<br />

Beispiel:<br />

Addition von 4 Zahlen: x = 0101, y = 0011, z = 0100, w = 0001<br />

Carry-Save-Addiernetze<br />

Anzahl der Additionsschritte ist abhängig von<br />

• Der Anzahl der zu addierenden Zahlen (nicht der Anzahl der<br />

Stellen)<br />

Dazu noch mal das Beispiel:<br />

Addition von 4 Zahlen: x = 0101, y = 0011, z = 0100, w = 0001<br />

Addition muss durchgeführt werden bis der Übertrag = 0000 ist<br />

52<br />

51<br />

5

Addiernetze - Carry-Save-<br />

Addiernetze<br />

Berechnungen = Carry-Save-Addierbausteine (CSA),<br />

reduzieren drei Summanden auf zwei Summanden,<br />

(d. h. eine „Summe“ <strong>und</strong> einen Übertrag)<br />

Realisierung durch nebeneinander geschaltete Volladdierer<br />

möglich<br />

Addiernetze - Carry-Save-<br />

Addiernetze<br />

53<br />

54<br />

6

Addiernetze - Carry-Save-<br />

Addiernetze<br />

Allgemein benötigt<br />

man m-2 CSA-<br />

Bausteine,<br />

um m Summanden<br />

zu addieren.<br />

Conditional-Sum-Addierer<br />

Beschleunigung der Berechnung durch red<strong>und</strong>ante<br />

Hardware<br />

55<br />

56<br />

7

Addiernetze - Multiplizierer<br />

Multiplikation ganzer Zahlen lässt sich<br />

mit Hilfe wiederholter Addition<br />

durchführen.<br />

Multiplikation kann<br />

folglich mit<br />

Schiebeoperationen<br />

<strong>und</strong> Additionen<br />

realisiert werden:<br />

Addiernetze - Multiplizierer<br />

Schaltet man also n-2<br />

CSA-Bausteine<br />

hintereinander,<br />

können n Additionen<br />

durchgeführt werden:<br />

57<br />

58<br />

8

Addiernetze - Multiplizierer<br />

Vorherige Technik sehr langsam, da Additionen sequenziell<br />

� CSA-Baustein kann immer erst dann addieren, wenn er die Ergebnisse<br />

von seinem Vorgänger erhalten hat.<br />

� 4-zu-2-Bausteinen<br />

Bisherige Schaltungen<br />

• Comparator<br />

• Decoder<br />

• Encoder<br />

• Shifter (Stellenverschiebung nach links <strong>und</strong> rechts)<br />

• Multiplexer<br />

• Demultiplexer<br />

• Addierer/Subtrahierer<br />

59<br />

60<br />

9

Bisherige Schaltungen<br />

Diese werden benötigt, um eine Arithmetik-Logik-<br />

Einheit zu erstellen,<br />

• diese soll als Eingang zwei Eingabewerte A <strong>und</strong> B<br />

haben,<br />

• Eine Funktion soll ausgeführt werden: A and B, A or<br />

B, not B, A+B (arithmetische Addition),<br />

• welche Funktion realisiert wird, soll durch<br />

Funktionseingänge bestimmt werden<br />

Arithmetic Logic Units (1)<br />

Eine 1-Bit ALU<br />

(aufgr<strong>und</strong> der<br />

Übersichtlichkeit),<br />

analog für<br />

8-Bit, 16-Bit, 32-Bit,<br />

64-Bit, …<br />

61<br />

62<br />

10

Arithmetic Logic Units (2)<br />

• Einfache Lösung: Verbindung von 8 1-bit ALUs zur Realisierung einer 8-bit ALU.<br />

• (Aufgr<strong>und</strong> der einfachen Darstllung wurden einige Eingänge weggelassen:<br />

ENA, ENB (= enable A bzw B))<br />

Logische Bausteine – Gatter<br />

63<br />

64<br />

11

Literatur<br />

� Helmut Herold / Bruno Lurz / Jürgen Wohlrab:<br />

Gr<strong>und</strong>lagen der Informatik, Pearson Studium, 2006<br />

� Bernd Becker / Rolf Drechsler / Paul Molitor: Technische<br />

Informatik – Eine Einführung, Pearson Studium, 2005<br />

� Computerarchitektur. Strukturen - Konzepte - Gr<strong>und</strong>lagen<br />

(Geb<strong>und</strong>ene Ausgabe) von Andrew S. Tanenbaum, Pearson<br />

Studium, 2005<br />

65<br />

12