Gliederung

Gliederung Gliederung

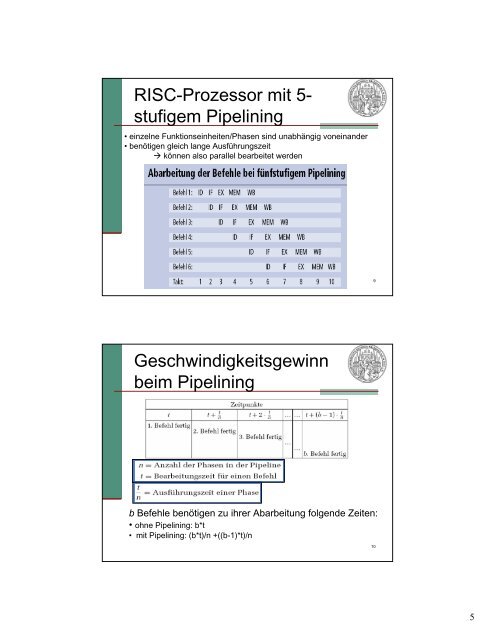

Phasen beim Pipelining Fließbandverarbeitung: Z.B. Befehl in 5 Phasen abarbeiten: • Phase 1: IF = Instruction Fetch nächsten Befehl aus dem Programmspeicher holen • Phase 2: ID = Instruction Decode dekodieren des Befehls, Operanden aus Registern holen • Phase 3: Ex = Execute/address calculation Ausführen der Operation und Berechnen der Adresse • Phase 4: MEM = Memory access Abspeichern des Ergebnisses • Phase 5: WB = Write back Evtl. Schreiben des Ergebnisses in Register Manche Befehle benötigen weniger als 5 Phasen: Erzeugt Befehl z.B. kein Ergebnis, entfallen die letzten beiden Phasen. RISC-Prozessor mit 5stufigem Pipelining Moderne Prozessoren haben nicht 5, sondern bis zu 20 Phasen, die durch eigene Funktionseinheiten realisiert sind 7 8 4

RISC-Prozessor mit 5stufigem Pipelining • einzelne Funktionseinheiten/Phasen sind unabhängig voneinander • benötigen gleich lange Ausführungszeit � können also parallel bearbeitet werden Geschwindigkeitsgewinn beim Pipelining b Befehle benötigen zu ihrer Abarbeitung folgende Zeiten: • ohne Pipelining: b*t • mit Pipelining: (b*t)/n +((b-1)*t)/n 9 10 5

- Seite 1 und 2: Rechnersysteme, Vorlesung 14: Cache

- Seite 3: Vor- und Nachteile von CISC bzw. RI

- Seite 7 und 8: Daten-Hazards beim Pipelining 2. M

- Seite 9 und 10: Control-Hazards beim Pipelining 2.

- Seite 11 und 12: Überblick: Speicherhierarchie 1-10

- Seite 13 und 14: Verfahren: write-through � Cache

- Seite 15 und 16: Verfahren: write-back � Cache Mis

- Seite 17 und 18: Verfahren: write-allocation � Ein

RISC-Prozessor mit 5stufigem<br />

Pipelining<br />

• einzelne Funktionseinheiten/Phasen sind unabhängig voneinander<br />

• benötigen gleich lange Ausführungszeit<br />

� können also parallel bearbeitet werden<br />

Geschwindigkeitsgewinn<br />

beim Pipelining<br />

b Befehle benötigen zu ihrer Abarbeitung folgende Zeiten:<br />

• ohne Pipelining: b*t<br />

• mit Pipelining: (b*t)/n +((b-1)*t)/n<br />

9<br />

10<br />

5