Grundlagen der Rechnerarchitektur (GRA) / Technische Informatik ...

Grundlagen der Rechnerarchitektur (GRA) / Technische Informatik ...

Grundlagen der Rechnerarchitektur (GRA) / Technische Informatik ...

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

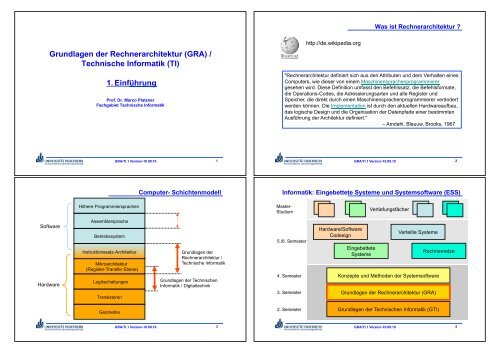

<strong>Grundlagen</strong> <strong>der</strong> <strong>Rechnerarchitektur</strong> (<strong>GRA</strong>) /<br />

<strong>Technische</strong> <strong>Informatik</strong> (TI)<br />

Software<br />

Hardware<br />

1. Einführung<br />

Prof. Dr. Marco Platzner<br />

Fachgebiet <strong>Technische</strong> <strong>Informatik</strong><br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Höhere Programmiersprachen<br />

Assemblersprache<br />

Betriebssystem<br />

Instruktionssatz-Architektur<br />

Mikroarchitektur<br />

(Register-Transfer Ebene)<br />

Logikschaltungen<br />

Transistoren<br />

Geometrie<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Computer- Schichtenmodell<br />

<strong>Grundlagen</strong> <strong>der</strong><br />

<strong>Rechnerarchitektur</strong> /<br />

<strong>Technische</strong> <strong>Informatik</strong><br />

<strong>Grundlagen</strong> <strong>der</strong> <strong>Technische</strong>n<br />

<strong>Informatik</strong> / Digitaltechnik<br />

1<br />

3<br />

http://de.wikipedia.org<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Was ist <strong>Rechnerarchitektur</strong> ?<br />

"<strong>Rechnerarchitektur</strong> definiert sich aus den Attributen und dem Verhalten eines<br />

Computers, wie dieser von einem Maschinensprachenprogrammierer<br />

gesehen wird. Diese Definition umfasst den Befehlssatz, die Befehlsformate,<br />

die Operations-Codes, die Adressierungsarten und alle Register und<br />

Speicher, die direkt durch einen Maschinensprachenprogrammierer verän<strong>der</strong>t<br />

werden können. Die Implementation ist durch den aktuellen Hardwareaufbau,<br />

das logische Design und die Organisation <strong>der</strong> Datenpfade einer bestimmten<br />

Ausführung <strong>der</strong> Architektur definiert."<br />

– Amdahl, Blauuw, Brooks, 1967<br />

<strong>Informatik</strong>: Eingebettete Systeme und Systemsoftware (ESS)<br />

Master-<br />

Studium<br />

5./6. Semester<br />

4. Semester<br />

3. Semester<br />

2. Semester<br />

Hardware/Software<br />

Codesign<br />

Eingebettete<br />

Systeme<br />

Vertiefungsfächer<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Verteilte Systeme<br />

<strong>Grundlagen</strong> <strong>der</strong> <strong>Rechnerarchitektur</strong> (<strong>GRA</strong>)<br />

Rechnernetze<br />

Konzepte und Methoden <strong>der</strong> Systemsoftware<br />

<strong>Grundlagen</strong> <strong>der</strong> <strong>Technische</strong>n <strong>Informatik</strong> (GTI)<br />

2<br />

4

Master-<br />

Studium<br />

Studienmodell<br />

Mikroelektronik<br />

5./6. Semester<br />

Vertiefung<br />

Mikrosystem-<br />

technik<br />

4. Semester<br />

3. Semester<br />

2. Semester<br />

Elektrotechnik: Mikrosystemtechnik und Mikroelektronik<br />

Schaltungstechnik<br />

(Pflicht)<br />

Wahlpflicht-<br />

katalog, z.B.<br />

Vertiefungsfächer<br />

Mikrosystemtechnik<br />

Qualitätssicherung für (WP)<br />

!elektronische Systeme (WP)<br />

<strong>Technische</strong> <strong>Informatik</strong> (TI) Laborpraktikum B<br />

Digitaltechnik (DT)<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Entwurf !elektronischer<br />

Systeme (WP)<br />

• http://www.upb.de/cs/gra-ti.html<br />

– aktuelle Informationen zur Lehrveranstaltung, Vorlesungsunterlagen<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Organisation<br />

• Übung<br />

– Beginn: 25. Oktober 2010<br />

– kleine Übungsgruppen (20 Personen)<br />

– Aufgaben vorher lösen, bei <strong>der</strong> Übung an <strong>der</strong> Tafel vorrechnen und diskutieren<br />

– In den Übungen können bis zu 10% Bonuspunkte erreicht werden.<br />

– Es gibt 12 Gruppen. Übungstermine und Räume auf <strong>der</strong> web page.<br />

Bitte melden Sie sich auf <strong>der</strong> web page für eine Übungsgruppe an (koaLA).<br />

• Wichtig (!)<br />

– zu den Übungen vorbereitet kommen<br />

– die Aufgabenstellungen ausgedruckt mitbringen<br />

5<br />

7<br />

Master-<br />

Studium<br />

5./6. Semester<br />

4. Semester<br />

3. Semester<br />

2. Semester<br />

Ingenieurinformatik - Elektrotechnik / Maschinenbau<br />

Projektgruppe <strong>Informatik</strong><br />

Projektgruppe E-Technik<br />

Wahlpflichtfächer E-Technik/<strong>Informatik</strong><br />

z.B. Mikrosystemtechnik und Mikroelektronik<br />

Praktikum Ingenieurinformatik<br />

Konzepte und Methoden <strong>der</strong> Systemsoftware<br />

<strong>Grundlagen</strong> <strong>der</strong> <strong>Rechnerarchitektur</strong> (<strong>GRA</strong>)<br />

<strong>Grundlagen</strong> <strong>der</strong> <strong>Technische</strong>n <strong>Informatik</strong> (GTI)<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Wahlpflicht-<br />

fächer<br />

Schaltungstechnik Entwurf !elektronischer<br />

Mikrosystemtechnik<br />

Systeme<br />

Qualitätssicherung für<br />

!elektronische Systeme<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Organisation<br />

• Freiwilliges Tutorium/Praktikum<br />

– Variante "VHDL-Basics", Entwurf von digitalen Schaltungen auf GTI/DT-Niveau,<br />

Wie<strong>der</strong>holen von VHDL als Vorbereitung auf die GTI/DT Klausur<br />

– Variante "Prozessor-Entwurf", Implementierung eines kleinen RISC-Prozessors,<br />

Vertiefung des <strong>GRA</strong>/TI-Stoffes für Interessierte<br />

– Tutorium/Praktikum findet in <strong>der</strong> zweiten Semesterhälfte im Raum P1.7.09 statt.<br />

– Anmeldung siehe web page.<br />

• Klausuren<br />

– Ende WS10/11 findet eine Klausur GTI/DT und eine Klausur <strong>GRA</strong>/TI statt.<br />

– Der Bonus aus den Übungen wird zur jeweiligen Klausur addiert.<br />

6<br />

8

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Das Betreuerteam<br />

• Vorlesung: Marco Platzner, P1.7.08.1, 60-5250, platzner@upb.de<br />

• Übungen:<br />

Koordinator: Jörg Stöcklein, F1.319, ozone@upb.de<br />

Gruppenleiter: Alexan<strong>der</strong> Boschmann, Thomas Glarner,<br />

Andreas Martens, Simon Oberthür, Michael Schnittger,<br />

Matthias Strotmeier, Jürgen Tessmann<br />

• Tutorium/Praktikum:<br />

Koordinator: Heiner Giefers, P1.7.08.3, 60-5395, hgiefers@upb.de<br />

Betreuer: Heiner Giefers, Viktor Fröse<br />

• William Stallings. Computer Organization and<br />

Architecture, 5th Edition, Prentice Hall, 2002,<br />

ISBN 0-1304-9307-4<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Weitere Literatur<br />

• John L. Hennessy and David A. Patterson.<br />

Computer Architecture: A Quantitative Approach.<br />

3rd Edition, Morgan Kaufmann, 2003,<br />

ISBN 1-55860-724-2<br />

9<br />

11<br />

Literatur (im Semesterapparat "GTI+<strong>GRA</strong>" <strong>der</strong> Bibliothek)<br />

• David A. Patterson, John L. Hennessy.<br />

Computer Organization And Design. 3rd Edition,<br />

Elsevier / Morgan Kaufmann, 2005, ISBN 1-55860-604-1<br />

(wenn nicht an<strong>der</strong>s angegeben, stammen die Abbildungen in<br />

den Folien aus diesem Buch, © Elsevier 2005)<br />

Deutsche Ausgabe, herausgegeben von A.Bode,<br />

W.Karl und T.Ungerer, Spektrum Akademischer<br />

Verlag, September 2005, ISBN 3-8274-1595-0<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

10<br />

Lernziele<br />

• Vorlesung<br />

Logischer und physikalischer Aufbau mo<strong>der</strong>ner Rechner mit einer<br />

Schwerpunktsetzung auf Prozessorarchitekturen, Betrachtung <strong>der</strong><br />

Instruktionssatzarchitektur (Programmiermodell, Unterstützung von<br />

Software) als auch des Prozessor-Entwurfs (Datenpfad und<br />

Kontroller, Nutzung von Parallelität)<br />

• Übungen<br />

Vertiefung des Vorlesungsstoffs durch Ausarbeitung von Beispielen<br />

und Erstellen von Assemblerprogrammen<br />

• Tutorium/Praktikum<br />

Variante "VHDL-Basics": Praktische Fertigkeiten in VHDL<br />

Variante "Prozessor-Entwurf": Praktische Fertigkeiten in VHDL,<br />

Vertiefung des Vorlesungsstoffs<br />

12

1. Einführung<br />

2. Instruktionssatzarchitektur und Assembler<br />

3. Leistungsbewertung<br />

4. Prozessorentwurf: Datenpfad und Kontroller<br />

5. Pipelining<br />

6. Speicherhierarchie<br />

7. Ein/Ausgabe<br />

8. Prozessorarchitektur für Fortgeschrittene<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Inhalt <strong>der</strong> Vorlesung<br />

13<br />

1.1 Computertypen<br />

Anzahl verkaufter Prozessoren (embedded, " 32 bit) bzw. Systeme (desktop, server)<br />

15<br />

1. Einführung<br />

1.1 Computertypen<br />

1.2 Technologie, Kosten, Trends<br />

1.3 Grundstruktur eines Computers<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Inhaltsverzeichnis<br />

Instruktionssatzarchitekturen<br />

Anzahl verkaufter Prozessoren (" 32 bit)<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

14<br />

ca. 80% davon<br />

für Mobiltelefone<br />

16

Monitor<br />

Tastatur<br />

Instruktionscache<br />

Floating-Point<br />

und Multimedia-<br />

Datenpfad<br />

Integer-<br />

Datenpfad<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Desktop Computer<br />

Computer-Gehäuse<br />

(Desktop Tower)<br />

Maus<br />

Mikrophotographie Pentium 4 Prozessor<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

17<br />

Datencache<br />

Sekundärer<br />

Cache, Speicher-<br />

interface<br />

19<br />

Lüfter<br />

Netzteil<br />

Motherboard<br />

(Prozessor, Speicher, Anschlüsse für I/O)<br />

Chipherstellung<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Im Gehäuse<br />

DVD-Laufwerk<br />

Festplatte<br />

1.2 Technologie, Kosten, Trends<br />

siehe GTI/DT: Kapitel 7, Technologische Realisierung<br />

18<br />

20

© Elsevier 2003<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Preisentwicklung DRAM<br />

Workstation Performance<br />

Performance relativ zu VAX-11/780, Integer-Programme<br />

21<br />

23<br />

Preise für Intel Pentium III<br />

© Elsevier 2003<br />

Preisentwicklung Prozessoren<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

1.3 Grundstruktur eines Computers<br />

• Ein Computer besteht aus Prozessor + Speicher + Ein/Ausgabe.<br />

• Der Speicher besteht aus Worten fester Länge und enthält Daten<br />

und Instruktionen.<br />

– Die Idee, nicht nur die Daten son<strong>der</strong>n auch die Instruktionen als Zahlen im<br />

Speicher abzulegen, wird meist John von Neumann zugeschrieben und als<br />

von Neumann Konzept (o<strong>der</strong> stored program concept) bezeichnet. Man spricht<br />

auch von einer von Neumann <strong>Rechnerarchitektur</strong>.<br />

• Der Prozessor besteht aus Rechenwerk und Steuerwerk.<br />

– Rechen- und Steuerwerk zusammen werden historisch als Central Processing Unit<br />

(CPU) bezeichnet.<br />

– In einem speziellen Register, dem Program Counter (PC, Befehlszähler), steht die<br />

Speicheradresse <strong>der</strong> auszuführenden Instruktion.<br />

– Typischerweise befinden sich im Rechenwerk weitere Register, da Rechenopera-<br />

tionen mit Registern viel schneller ausführbar sind als mit Operanden im Speicher.<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

22<br />

24

Prozessor<br />

Rechenwerk<br />

Register<br />

Instruktions-<br />

register<br />

Steuerwerk<br />

Prozessor<br />

Rechenwerk<br />

Register<br />

Instruktions-<br />

register<br />

Steuerwerk<br />

PC<br />

PC<br />

1<br />

Adress-<br />

register<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Prinzip-Blockschaltbild<br />

Daten<br />

Speicher<br />

Daten<br />

und<br />

Instruktionen<br />

Adresse<br />

Instruktion aus dem Speicher holen<br />

Adress-<br />

register<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Daten<br />

Speicher<br />

Daten<br />

und<br />

Instruktionen<br />

Adresse<br />

25<br />

27<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

Instruktion aus dem Speicher holen<br />

Instruktion dekodieren<br />

Operanden holen (aus Speicher o<strong>der</strong> Register)<br />

Ausführen <strong>der</strong> Instruktion<br />

Resultat abspeichern (im Speicher o<strong>der</strong> Register)<br />

Nächste Instruktion bestimmen<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Instruktionszyklus<br />

– Je nach Art <strong>der</strong> Instruktion und des Prozessors können einzelne Schritte<br />

dieses Zyklus zusammengefasst o<strong>der</strong> übersprungen werden.<br />

Prozessor<br />

Rechenwerk<br />

Register<br />

Instruktions-<br />

register<br />

Steuerwerk<br />

PC<br />

Adress-<br />

register<br />

2<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

26<br />

Instruktion dekodieren<br />

Daten<br />

Speicher<br />

Daten<br />

und<br />

Instruktionen<br />

Adresse<br />

28

Prozessor<br />

Rechenwerk<br />

Register<br />

Instruktions-<br />

register<br />

Steuerwerk<br />

PC<br />

Adress-<br />

register<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Daten<br />

Operanden holen<br />

Speicher<br />

Daten<br />

und<br />

Instruktionen<br />

Adresse<br />

– Operanden können auch in Registern stehen.<br />

– Instruktionen können keinen, einen o<strong>der</strong> mehrere Operanden haben.<br />

Prozessor<br />

Rechenwerk<br />

Register<br />

Instruktions-<br />

register<br />

Steuerwerk<br />

PC<br />

Adress-<br />

register<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

3<br />

29<br />

Resultat abspeichern<br />

Daten<br />

– Resultate können auch in Register geschrieben werden.<br />

5<br />

Speicher<br />

Daten<br />

und<br />

Instruktionen<br />

Adresse<br />

31<br />

Prozessor<br />

Rechenwerk<br />

Register<br />

Instruktions-<br />

register<br />

Steuerwerk<br />

PC<br />

4<br />

Adress-<br />

register<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Ausführen <strong>der</strong> Instruktion<br />

Daten<br />

Speicher<br />

Daten<br />

und<br />

Instruktionen<br />

Adresse<br />

– Das Operationswerk führt zB. Arithmetik- o<strong>der</strong> Logikoperationen aus.<br />

Prozessor<br />

Rechenwerk<br />

Register<br />

Instruktions-<br />

register<br />

Steuerwerk<br />

PC<br />

6<br />

Nächste Instruktion bestimmen<br />

Adress-<br />

register<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

Daten<br />

Speicher<br />

Daten<br />

und<br />

Instruktionen<br />

Adresse<br />

– Mit hoher Wahrscheinlichkeit ist die nächste auszuführende Instruktion an <strong>der</strong><br />

nächsthöheren Adresse im Speicher zu finden. Deshalb wird standardmässig<br />

<strong>der</strong> PC um 1 erhöht. Ausnahme: Sprunginstruktionen.<br />

30<br />

32

• Klassische Sichtweise<br />

– Ein- und Ausgabe<br />

– Speicher<br />

– Rechenwerk und Steuerwerk (Prozessor)<br />

• Mo<strong>der</strong>nere Sichtweise<br />

– Ein- und Ausgabe<br />

– Speicher<br />

– Datenpfad und<br />

Kontroller<br />

Komponenten eines Rechners<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

33<br />

Compiler<br />

Assembler<br />

Assembler und Maschinensprache<br />

<strong>GRA</strong>/TI.1 Version-10.09.10<br />

34