Design Flow und Verilog

Design Flow und Verilog

Design Flow und Verilog

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

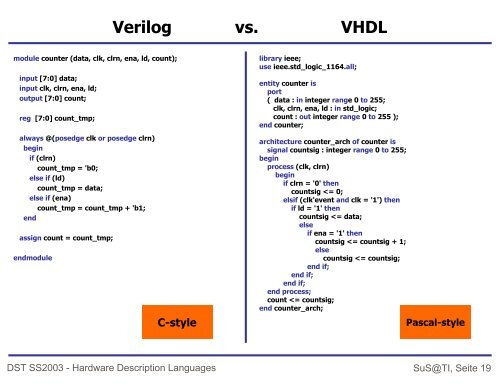

<strong>Verilog</strong>vs. VHDLmodule counter (data, clk, clrn, ena, ld, count);input [7:0] data;input clk, clrn, ena, ld;output [7:0] count;reg [7:0] count_tmp;always @(posedge clk or posedge clrn)beginif (clrn)count_tmp = 'b0;else if (ld)count_tmp = data;else if (ena)count_tmp = count_tmp + 'b1;endassign count = count_tmp;endmoduleC-stylelibrary ieee;use ieee.std_logic_1164.all;entity counter isport( data : in integer range 0 to 255;clk, clrn, ena, ld : in std_logic;count : out integer range 0 to 255 );end counter;architecture counter_arch of counter issignal countsig : integer range 0 to 255;beginprocess (clk, clrn)beginif clrn = '0' thencountsig