Chipmontage auf MID (Molded Interconnect Device) â Ein Weg zu ...

Chipmontage auf MID (Molded Interconnect Device) â Ein Weg zu ...

Chipmontage auf MID (Molded Interconnect Device) â Ein Weg zu ...

- Keine Tags gefunden...

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

T e c h n o l o g i eDr. Werner Hunziker<strong>Chipmontage</strong> <strong>auf</strong> <strong>MID</strong> (<strong>Molded</strong> <strong>Interconnect</strong> <strong>Device</strong>) –<strong>Ein</strong> <strong>Weg</strong> <strong>zu</strong> Chipmodulen höherer FunktionalitätDie <strong>MID</strong> (<strong>Molded</strong> <strong>Interconnect</strong> <strong>Device</strong>) – Technologieerlaubt die Erzeugung von nichtplanaren <strong>Chipmontage</strong>substraten.Diese können nicht nur als mehrdimensionaleChipträger agieren, sondern auch noch weitereFunktionen beinhalten, und z.B. einen direkten Bestandteildes Gehäuses oder Steckers darstellen. Fürdie <strong>Chipmontage</strong> <strong>auf</strong> diese speziell geformten Kunststoffträgerwerden nun, basierend <strong>auf</strong> den Technikenfür planare Substrate, Prozesse entwickelt, welcheeine industrielle Chipbestückung der <strong>MID</strong> für verschiedensteAnwendungen erlauben. Damit lassen sichz.B. aus einem Teil anwendungsspezifische, kompakteSensormodule realisieren, welche den Messwert<strong>auf</strong>nehmeran einer räumlich geeigneten Stelle fixierenund gleichzeitig Zuleitungen und Interface <strong>zu</strong>m Gesamtsystembeinhalten.HARTING tec.News 13-I-2005

<strong>MID</strong>s<strong>Molded</strong> <strong>Interconnect</strong> <strong>Device</strong>s (<strong>MID</strong>s) sind spritzgegosseneKunststoffteile, welche elektrische Leiterbahnentragen. Sie stellen somit eine Art dreidimensionale Leiterplattendar. Elektrische Verbindungen können dabei„um die Ecke“ führen, und Bauteile können in verschiedenenRaumrichtungen angeordnet werden. Neben dieserRaumausnut<strong>zu</strong>ng können durch die Spritzgussform weitereFunktionen erzeugt werden, so kann es z.B. direktTeil des Gehäuses sein, spezielle geometrische Formen,wie Vertiefungen, Kanäle, Öffnungen, etc. z.B. für Messwert<strong>auf</strong>nehmerkönnen direkt integriert werden, wieauch Ankontaktierungen, Justiernocken oder Montagehilfenfür die nächste Verpackungsstufe.Als Grundkörper finden diverse Kunststoffe wie PBT, PPund LCP Verwendung.Zur Erzeugung feiner dreidimensionaler Leiterbahnenwerden im Wesentlichen drei Verfahren angewendet:LDS (Laser Direct Structuring), LSS (Laser SubtractiveStructuring) und zwei Komponenten (2K)-Spritzguss.Beim LDS wird der mit einem Metallkomplex verseheneKunststoff mit einem Laser beschrieben. Dies führt <strong>zu</strong>einer örtlichen Aktivierung des Metallkomplexes, wosich der Kunststoff anschließend in chemischen Bädernmetallisieren lässt.Beim LSS-Verfahren wird <strong>zu</strong>erst die gesamte Kunststoffoberflächechemisch aktiviert und metallisiert. DieStukturierung erfolgt dann durch Laserablation und/oder Belichtung mit anschließenden Ätzprozessen, umdie Leiterbahnen <strong>zu</strong> trennen. Dies stellt somit einen subtraktivenProzess dar.Beim 2K-Spritzguss werden in einem zweistufigen Spritzverfahrenzwei verschiedene Kunststoffe so ineinandergespritzt, dass an der Oberfläche das Leiterbahnmusteraus den zwei Komponenten entsteht. Werden ein chemischgut metallisierbarer und ein „inerter“ Kunststoffverwendet, erzeugt die chemische Metallabscheidungdirekt die entsprechende Leiterbahnstruktur. <strong>Ein</strong>e Laserstrukturierungjedes einzelnen Teiles erübrigt sich.Die Abbildung eines solchen im LDS-Verfahren hergestellten<strong>MID</strong>-Teiles mit verschiedenen nichtplanarenLeiterbahnen und elektrischen Durchkontaktierungenim Größenvergleich mit einem Streichholz findet sich imvorgehenden Artikel <strong>auf</strong> Seite 16.CHIPMONTAGETECHNIKENDie <strong>Chipmontage</strong> beinhaltet die mechanische und elektrischeVerbindung des ursprünglichen, noch ungeschütztenSilizium (Si)-Chips <strong>zu</strong> einem Gehäuse oder einemMontagesubstrat, inklusive einem ersten Schutz gegenverschiedene Umwelteinflüsse. Die ursprünglichen Montagetechnikenwurden entwickelt, um einzelne Chipsin stabilen Gehäusen <strong>zu</strong> verpacken. Der Druck hin <strong>zu</strong>größeren Packungsdichten, d. h. kleinerem Platzbedarf,führte <strong>zu</strong>r Entwicklung einer Vielzahl von verschiedenen<strong>Chipmontage</strong>techniken im Bereich Flip-Chip. Abbildung1 gibt eine Kurzübersicht über die heute hauptsächlicheingesetzten Techniken. Die Hauptunterschiede zwischenDrahtbonden und Flip-Chip liegen im Platzbedarf,Prozessabl<strong>auf</strong> sowie in den Stabilitätsanforderungen. DasDrahtbonden braucht durch die nach außen geführtenDrähte und den Glob Top viel Platz, weist einen sequentiellenVerbindungsprozess jedes einzelnen Anschlusses<strong>auf</strong> und zeigt eine gute Stabilität durch die „beweglichen“elektrischen Drahtverbindungen. Hauptvorteil der Flip-Chip-Prozesse ist die Platzersparnis und die paralleleVerbindung aller Anschlüsse in einem Schritt.Für die <strong>Chipmontage</strong> <strong>auf</strong> <strong>MID</strong>s werden bei harting momentandie zwei in Abbildung 1 hervorgehobenen undanschließend beschriebenen Technologien entwickeltund angewendet. Das Drahtbonden stellt einerseits die<strong>auf</strong> planaren Substraten etablierteste Technik dar. Andererseitsbietet es den Vorteil einer hohen Flexibilitätbzgl. verschiedener Chips, welche alle ohne Zusatzprozessedrahtbondbar sind, sowie größere Freiheiten beimSubstratlayout durch die variable Position und Länge derDrahtverbindungen. Die Verwendung eines Klebeprozessesbei Flip-Chip-Montagen liegt primär darin begründet,dass in vielen Fällen das <strong>MID</strong>-Bauteil selbst in einemspäteren Montageschritt noch bleifrei verlötet werdensoll, und noch höhere Löttemperaturen <strong>zu</strong>r Erzielungeiner Löthierarchie <strong>auf</strong> dem <strong>MID</strong> durch die maximalenTemperaturen der verwendeten Kunststoffe nicht möglichsind.HARTING tec.News 13-I-2005

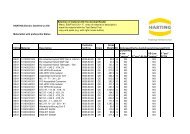

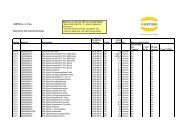

<strong>Chipmontage</strong>technikenDrahtbondenFlip-ChipThermosonicBonden (TS)UltraschallBonden (US)KlebenIsotrop leitenderKlebstoff (ICA)Anisotrop leitenderKlebstoff (ACA)LötenBleihaltiges Lot mit/ohne FlussmittelBleifreies Lot mit/ohne FlussmittelNichtleitenderKlebstoff (NCA)Abb. 1: Kurzübersicht über <strong>Chipmontage</strong>verfahren;hervorgehoben sind die hier für die <strong>MID</strong>-Bestückung näher beschriebenen ProzesseDRAHTBONDENBeim Drahtbondprozess werden die Chipanschlusspadsdes <strong>auf</strong> das Substrat geklebten Chips mit einem sehr feinenMetalldraht (meist Au oder Al mit Durchmessern imBereich 25-70 µm) mit den Leiterbahnen <strong>auf</strong> dem Substratverbunden. Diese Verbindungen erfolgen durch lokalesVerschweißen des Drahtes mit der darunterliegendenMetallisierung. Die erforderliche Energie wird entwederrein durch Ultraschallschwingungen des Bondtools (US-Verfahren), oder noch durch <strong>zu</strong>sätzliche Erwärmung (TS-Verfahren) eingebracht. Während sich Al-Drähte rein mitUltraschall bei Raumtemperatur bonden lassen, sind fürAu-Drähte Temperaturen von über 100 °C erforderlich,was den <strong>Ein</strong>satz <strong>auf</strong> den Kunststoffsubstraten durch ihreschlechte Wärmeleitung und leichtere Verformbarkeitbei höheren Temperaturen erschwert.Die Übertragung des <strong>auf</strong> planaren Substraten etabliertenDrahtbondprozesses <strong>auf</strong> <strong>MID</strong>-Teile zeigt sich im Wesentlichenin zwei Punkten als kritisch. Um eine gute Bondbarkeit<strong>zu</strong> erreichen, sind eine gute Ultraschallübertragungund nicht <strong>zu</strong> raue Metallschichten erforderlich.Die gute Ultraschalleinbringung erfordert eine ‚harte’Auflage des Bondtools. Da<strong>zu</strong> bedarf es einerseits einerguten Fixierung des Bauteiles selbst, was bei diesenmeist kleinen <strong>MID</strong>-Bauteilen <strong>zu</strong> recht <strong>auf</strong>wendigen Halterungenführen kann. Andererseits wird eine genügendeSteifigkeit des Bauteiles selbst benötigt, was durchdie Art des verwendeten Kunststoffes, das Layout unddie Metallisierung beeinflusst wird.Die Forderung nach glatten Metallschichten steht imWiderspruch <strong>zu</strong>r guten Haftung der Metallschicht <strong>auf</strong>der Kunststoffoberfläche. Nur eine gewisse Rauigkeitgarantiert eine genügende Haftfestigkeit. Außerdemführen die verschiedenen Metallisierungsverfahren <strong>zu</strong>unterschiedlich rauen Oberflächen. LDS-Schichten sindmomentan noch kaum industriell bondbar, jedoch werdendurch Variation von Laserparametern und Metallisierungl<strong>auf</strong>end starke Verbesserungen erzielt. Beim 2K-

Abb. 2: Testchip gebondet mit 33 µm dickem Al-Draht<strong>auf</strong> metallisiertes <strong>MID</strong>-Substratund LSS-Verfahren wird der entsprechende Kunststoffdirekt chemisch aktiviert und metallisiert, was die Erzeugungbondbarer Schichten mit genügend kleiner Rauigkeiterlaubt. Abbildung 2 zeigt einen Testchip, welcher<strong>auf</strong> ein derart metallisiertes <strong>MID</strong>-Substrat geklebt undanschließend mit dem US-Verfahren mit 33 µm dickemAl-Draht gebondet wurde.Beim Drahtbonden bringt die Verwendung von Spritzgussteilenals Montagesubstrate auch Vorteile, wie dasBeispiel in Abbildung 3 demonstriert. Es können z.B.einfach Kavitäten erzeugt werden, in welchen die Chipsmechanisch gut geschützt sind und der Glob Top einfachund platzsparend <strong>auf</strong>gebracht werden kann. Glob Top istdas Vergussmaterial, mit welchem Chip und Bonddrähteeingegossen werden, um diese <strong>zu</strong> stabilisieren und <strong>zu</strong>schützen. Bei planaren Substraten ist da<strong>zu</strong> häufig einZweischrittverfahren notwendig, bei dem um den Chipherum <strong>zu</strong>erst ein Damm <strong>auf</strong>gebracht wird, welcher danndas weite Zerfließen des über den Chip und Drähte verteiltenGlob Tops verhindert.NCA-FLIP-CHIPBei den Flip-Chip-Techniken wird der Chip umgedreht,und die dann <strong>auf</strong> der Unterseite liegenden elektrischenAnschlüsse direkt mit den geometrisch korrespondierendenLeiterbahnen verbunden. Die mechanische Befestigungmuss somit im gleichen räumlichen Bereich wiedie elektrischen Verbindungen erfolgen. Bei den meistenVerfahren (Löten und ICA = Isotropic Conductive Adhesive,isotrop leitender Klebstoff) erfolgen die beiden Schrittegetrennt, indem <strong>zu</strong>erst die elektrischen Verbindungendurch kleine Hügel aus Lot oder leitfähigem Kleber erzeugtund im Prozess (löten oder aushärten) die Kontaktehergestellt werden. Im zweiten Schritt werden dann Chipund Anschlüsse mit einem Underfill noch mechanischstabilisiert und geschützt. Beim ACA- und NCA-Prozess(ACA = Anisoptropic Conductive Adhesive, Anisotropleitender Klebstoff und NCA = NonConductive Adhesive,Nichtleitender Klebstoff) sind diese zwei Schritte ineinem vereint, indem der <strong>auf</strong> der gesamten Chipfläche<strong>auf</strong>gebrachte Kleber beim Aushärteprozess beide Funktionenerzeugt. In beiden Fällen sind elektrische leitendeErhöhungen (Bumps) <strong>auf</strong> den Chippads und/oder den Leiterbahnennotwendig, um die elektrische Kontaktierung<strong>zu</strong> gewährleisten. Beim ACA-Prozess enthält der Kleberwenige leitfähige Partikel, welche nur dort <strong>zu</strong> einer leitfähigenVerbindung führen, wo sie beim Montageprozessdurch die Bumps ‚eingeklemmt’ werden. Der NCA ist einelektrisch nicht leitender Kleber, welcher beim Aushärtenmit Druck und Wärme den direkten mechanischenund elektrischen Kontakt der Bumps <strong>zu</strong>r Gegenmetallisierunggewährleistet.Abb. 3: Drahtgebondeter Chip in der Vertiefungeines Spritzgussteils, welches gleichzeitig noch Justierhilfen(Noppen links) für weitere Montageschritte <strong>auf</strong>weistAbb. 4: Si-Testchip mit Au Stud-Bumps <strong>auf</strong> AnschlusspadsHARTING tec.News 13-I-2005

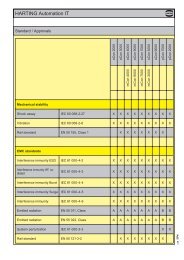

Abb. 6: Querschliff durch Flip-Chip montierten Chipin <strong>MID</strong>-Mulde mit elektrischen ZuleitungenFür die NCA-Flip-Chip-Montage <strong>auf</strong> den <strong>MID</strong>-Substratenwerden Chips verwendet, welche mit so genanntenAu Stud-Bumps versehen sind. Letztere werden mittelseines Standard Au-Drahtbondprozesses erzeugt, indemder Draht nach dem Setzen des ersten Bonds gleich abgeschnittenwird. In einem zweiten Schritt werden alleDrahtstücke <strong>auf</strong> gleiche Höhe gedrückt. Abbildung 4zeigt einen Testchip schräg von der Seite, <strong>auf</strong> welchemdie Anschlusspads mit solchen Stud-Bumps versehensind.Abb. 5: Mit NCA-Prozess-Flip-Chip montierter IC in <strong>MID</strong>-Muldemit nichtplanaren elektrischen ZuleitungenAuf dem <strong>MID</strong>-Substrat werden Leiterbahnen erzeugt,welche unter dem Chip <strong>zu</strong> den entsprechenden Anschlusspadsführen. Diese können <strong>auf</strong> <strong>MID</strong>s auch in Muldenhinein oder um Kanten herumführen, so dass Chips versenktoder räumlich dreidimensional angeordnet werdenkönnen. Abbildung 5 zeigt eine solche Flip-Chip-Montage,bei welcher der Chip in einer Mulde liegt und überdie Seitenwände elektrisch kontaktiert ist.Der NCA-Montageprozess hat den Vorteil eines einstufigenProzesses: Kontaktierung, Fixierung und ersterSchutz in einem Schritt. Nach dem Aufbringen des Klebersan der Chipposition wird der umgedrehte Chip soin den Kleber gedrückt, dass die Stud-Bumps <strong>auf</strong> dieentsprechenden Leiterbahnen gepresst werden und denelektrischen Kontakt erzeugen. Unter Aufrechterhaltungdes Drucks und Temperaturen im Bereich 150-200°C härtet der Kleber je nach Typ innerhalb von 10-30Sekunden aus. Die bei der Aushärtung <strong>auf</strong>tretendenSchrumpfkräfte bewirken sowohl eine stabile elektrischeals auch eine mechanische Verbindung des Chips.Des Weiteren ist auch die bereits nach unten gerichteteChipoberfläche eingegossen und somit geschützt. Abbildung6 zeigt einen Querschliff durch einen so montiertenChip in einer Mulde. Die <strong>auf</strong> den Chippads <strong>auf</strong>gebrachtenAu Stud-Bumps sind <strong>auf</strong> die <strong>auf</strong> dem <strong>MID</strong> mit demLDS-Verfahren erzeugten Leiterbahnen <strong>auf</strong>gedrückt und<strong>zu</strong>sammen mit dem Chip durch den Kleber fixiert.FAZITDie <strong>MID</strong>-Technologie <strong>zu</strong>r Herstellung nichtplanarer Bauteilträgermit beinahe beliebig geformten elektrischenLeiterbahnen hat sich in den letzten Jahren in vielen Bereichendes großen Anwendungsfeldes der Sensortechnikeinen Platz geschaffen. Mit der Bereitstellung von<strong>Chipmontage</strong>techniken für Nacktchips direkt <strong>auf</strong> <strong>MID</strong>-Substraten erweitert sich der Anwendungsbereich dieserneuen Technologie weiter. Sensoren können Platz sparendund häufig näher an der Messstelle platziert werdenund die Packungsdichte von Chips in dreidimensionalerAnordung kann weiter erhöht werden. Mit der l<strong>auf</strong>endenErweiterung von Montageprozessen <strong>auf</strong> <strong>MID</strong>-Substratenkomplettiert harting weiter den gesamten <strong>MID</strong>-Prozessvom Design <strong>zu</strong>m Endprodukt.Dr. Werner Hunzikerwww.HARTING-Mitronics.commit@HARTING.com

People | Power | PartnershipHARTING Mitronics AGLeugenestrasse 10 · CH-2500 Biel – SchweizTel. +49 5772 47-850 · Fax +49 5772 47-9131E-Mail: mit@HARTING.com · Internet: www.HARTING-Mitronics.com