Implementierung Massiv Paralleler Systeme - Institut für Informatik ...

Implementierung Massiv Paralleler Systeme - Institut für Informatik ...

Implementierung Massiv Paralleler Systeme - Institut für Informatik ...

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

<strong>Implementierung</strong><br />

<strong>Massiv</strong><br />

<strong>Paralleler</strong><br />

<strong>Systeme</strong><br />

Manfred Schimmler, Lars Wienbrandt, Sven Koschnicke<br />

<strong>Institut</strong> <strong>für</strong> <strong>Informatik</strong><br />

Lehrstuhl Technische <strong>Informatik</strong><br />

Christian-Albrechts-Universität zu Kiel<br />

1

Inhalt der Vorlesung<br />

1. Motivation und Einleitung<br />

2. Einführung in VHDL<br />

3. Automatenmodellierung mit VHDL<br />

4. Synthesefähiger Entwurf eines Mikroprozessors in VHDL<br />

5. FPGA-Technologie<br />

6. Taktung<br />

7. Parallelität<br />

8. Topologien und Komplexitätsmaße<br />

9. Parallele Architekturen 1 (Das Instruction Systolic Array)<br />

10.ISA-Prozessor-Architektur<br />

11.Parallele Hardware-Algorithmen 1 (Paralleles Merge)<br />

12.Parallele Hardware-Algorithmen 2 (Paralleles Sortieren)<br />

13.Parallele Hardware-Algorithmen 3 (Graphen-Algorithmen)<br />

14.Parallele Hardware-Algorithmen 4 (Brücken und FFT)<br />

15.Parallele Architekturen 2 (Vektorrechner)<br />

16.Parallele Architekturen 3 (Systolische Felder)<br />

17.Cloud Computing<br />

18. Der FPGA-basierte Parallelrechner Rivyera<br />

19. Rivyera API<br />

20. Bio-<strong>Informatik</strong> Algorithmen 1<br />

21. Bio-<strong>Informatik</strong> Algorithmen 2<br />

2

Was erwartet sie heute?<br />

1. Motivation<br />

Arten digitaler integrierter Schaltkreise<br />

Welche Zielarchitektur passt <strong>für</strong> welche Anwendung?<br />

Taxonomie der ICs<br />

Typen konfigurierbarer und rekonfigurierbarer Logik<br />

Ebenen beim Entwurf digitaler Schaltungen<br />

Entwurfsprozess<br />

Funktion der Hardwarebeschreibungssprache<br />

3

Arten digitaler integrierter Schaltungen<br />

• Diskrete Bauteile mit einer kleinen Anzahl einzelner Gattern zum<br />

Auflöten oder Aufstecken auf Platinen (z.B. in TTL, 7400)<br />

• Einfache fest konfigurierte Funktionsblöcke auf einem Chip ohne oder<br />

mit sehr begrenzter Möglichkeit der Programmierung (z.B. einfache<br />

Speicherchips, Zähler, Taschenrechner, Uhren)<br />

• Komplexe fest konfigurierte programmierbare Einheiten auf einem<br />

Chip (z.B. Mikroprozessoren, Mikrocontroller, Digitale Signal<br />

Prozessoren (DSPs), Massenspeicher mit integrierter Logik)<br />

• Kundenspezifisch konfigurierbare einfache Bausteine, z.B. PLA, FPLA<br />

(Programmable Logic Array, Field Programmable Logic Array)<br />

• Kundenspezifisch konfigurierbare komplexe Bausteine, z.B. FPGA<br />

(Field Programmable Gate Array)<br />

• Anwenderspezifische Integrierte Schaltkreise, ASICs<br />

4

Welche Zielarchitektur <strong>für</strong> welche Anforderung?<br />

Hauptkriterium: Datendominanz oder Kontrolldominanz?<br />

1. Beispiel: Die Steuerung der Einspritzung von Kraftstoff in einem<br />

Verbrennungsmotor<br />

2. Beispiel: Eine Grafikkarte<br />

3. Beispiel: Gesucht ist eine Hardwarelösung zum Angriff auf ein<br />

symmetrisches Verschlüsselungsverfahren, z.B. DES (Data<br />

Encryption Standard).<br />

4. Beispiel: Warum leisten Mikroprozessoren in datendominanten<br />

Anwendungen weniger als DSPs?<br />

5. Beispiel: Vektorprozessoren<br />

5

Welche Zielarchitektur <strong>für</strong> welche Anforderung?<br />

Hauptkriterium: Datendominanz oder Kontrolldominanz?<br />

1. Beispiel: Die Steuerung der Einspritzung von Kraftstoff in einem<br />

Verbrennungsmotor erfordert nicht viele (numerische) Berechnungen.<br />

Andererseits muss aber echtzeitig und zuverlässig reagiert werden. Es<br />

sind eine Reihe von Sondersituationen denkbar, die über spezielle<br />

Programme behandelt werden müssen. Die Art der Berechnung ist<br />

weitgehend ereignisgesteuert. Hier überwiegt die Kontrolle gegenüber<br />

der Datenverarbeitung, die Anwendung ist „kontrolldominant“.<br />

Für eine solche Anwendung verwendet man einen Mikrocontroller (was<br />

nichts anderes ist als ein auf Kosten optimierter Mikroprozessor).<br />

2. Beispiel: Eine Grafikkarte muss <strong>für</strong> Millionen von Pixeln dieselben<br />

Operationen durchführen, um einen Frame auf dem Bildschirm zu<br />

berechnen. Die Folge der Operationen ist fest vorgegeben, es gibt keine<br />

oder fast keine Sondersituationen und Interrupts. Der Datendurchsatz<br />

soll optimal sein, d.h. in einer festen Zeit sollen soviele (gleichartige)<br />

Berechnungen wie möglich gemacht werden. Eine solche Anwendung<br />

ist „datendominant“. Typische Zielarchitekturen hier sind DSPs oder<br />

Spezialprozessoren.<br />

6

Welche Zielarchitektur <strong>für</strong> welche Anforderung?<br />

3. Beispiel: Gesucht ist eine Hardwarelösung zum Angriff auf ein<br />

symmetrisches Verschlüsselungsverfahren, z.B. DES (Data Encryption<br />

Standard). Diese muss 2 56 mögliche Schlüssel einer Chiffre<br />

durchprobieren, um einen chiffrierten Text in den zugehörigen Klartext<br />

zurück zu übersetzen. Selbst schnellste Mikroprozessoren und sogar<br />

schnellste DSPs würden Jahrzehnte rechnen, um diese Aufgabe zu<br />

erfüllen. Dieses (ganz klar datendominierte) Anwendung erfordert eine<br />

individuelle Lösung, die speziell <strong>für</strong> diese Anwendung entwickelt wird.<br />

Man nennt eine solche Lösung „kundenspezifisch“, „application specific“<br />

oder „custom solution“. In diesem Falle könnte die Lösung eine<br />

Parallelarchitektur aus mehreren speziell <strong>für</strong> DES konfigurierten FPGAs<br />

sein, die mit deutlich höherem Durchsatz die möglichen Schlüssel<br />

durchprobieren können, als jeder Standardrechner. Oft werden mit<br />

solchen kundenspezifischen Lösungen Geschwindigkeiten erreicht, die<br />

sogar deutlich über denen von Superrechnern liegen.<br />

7

Welche Zielarchitektur <strong>für</strong> welche Anforderung?<br />

4. Beispiel: Warum leisten Mikroprozessoren in datendominanten<br />

Anwendungen weniger als DSPs?<br />

Mikroprozessoren sind „Alleskönner“, die <strong>für</strong> den Universaleinsatz<br />

optimiert sind. Sie haben aufwendige Pipelines, Branch-Prediction-<br />

Einheiten, Interrupt-Einheiten usw. die darauf ausgelegt sind,<br />

Unregelmäßigkeiten im Kontrollfluss effizient bearbeiten zu können.<br />

DSPs sind im Gegensatz dazu Rechenknechte. Sie haben (oft) viele<br />

Recheneinheiten, die parallel arbeiten können. Oft sind diese auch<br />

kombiniert, um spezielle Funktionen besonders schnell oder mit<br />

besonders hohem Durchsatz berechnen zu können. Ein Beispiel da<strong>für</strong><br />

ist eine Multiply-Add-Einheit, die viele Anwendungen in der linearen<br />

Algebra beschleunigen kann, z.B. Matrix-Multiplikation oder –Inversion.<br />

DSPs haben breite Datenleitungen (<strong>für</strong> Ein- und Ausgabe). Ein anderes<br />

Extrem in dieser Richtung sind die Netzwerkprozessoren, die darauf<br />

zugeschneidert sind, Anwendungen aus der modernen Digitalen<br />

Nachrichtenvermittlung zu beschleunigen.<br />

8

Welche Zielarchitektur <strong>für</strong> welche Anforderung?<br />

5. Beispiel: Vektorprozessoren verfügen über spezielle Einheiten, mit<br />

denen Vektoren verarbeitet werden können. Diese zeichnen sich durch<br />

eine besonders tiefe Pipeline aus. Ferner gibt es Register mit<br />

Vektorbreite und einen schnellen vektoriellen Speicherzugriff.<br />

Aufeinanderfolgende Operationen werden durch das sogenannte<br />

Chaining (Forewarding zwischen Operationen) beschleunigt.<br />

Vektorprozessoren waren in den 70-er und 80-er Jahren die ersten<br />

Superrechner. Heute verfügen viele Standardprozessoren über<br />

assoziierte Vektoreinheiten.<br />

9

Ein ASIC (Application Specific Integrated Circuit) ist ein<br />

anwendungsspezifischer integrierter Schaltkreis.<br />

Wenn es sich um einen Chip handelt, dessen sämtliche Transistoren<br />

und Leitungen frei vom Anwender entworfen, positioniert und<br />

dimensioniert werden, spricht man von einem Full-custom ASIC.<br />

Beim Full-Custom ASIC stehen dem Entwerfer alle Möglichkeiten zur<br />

Verfügung, die auch die Entwerfer von Mikroprozessoren (z.B. bei<br />

Intel oder Texas Instruments) benutzen (allerdings haben die kleineren<br />

Entwurfshäuser in der Regel nicht Zugang zu den jeweils besten<br />

Fabrikationsstätten, die in der Hand der großen Chiphersteller sind).<br />

Ein Beispiel <strong>für</strong> einen ASIC sehen wir auf der folgenden Folie. Die<br />

farbigen Striche und Rechtecke sind Leitungen in unterschiedlichen<br />

Materialien aus denen die Transistoren und Verbindungen aufgebaut<br />

werden.<br />

10

Full Custom Entwurf<br />

11

Full-custom<br />

ASIC-Entwurfsprozess<br />

Funktionale Beschreibung<br />

Floorplanning<br />

Design und Layout<br />

Design Rule Check<br />

Extraktion der Netzliste<br />

Simulation<br />

Electrical Rule Check<br />

Maskengenerierung<br />

Fertigung<br />

Test<br />

12

Wenn der Anwender sich beim Entwurf auf eine Menge von<br />

vorgegebenen Standardzellen beschränken kann und das Plazieren<br />

auf dem Chip (Placement) sowie das Verdrahten der Standardzellen<br />

untereinander (Routing) durch ein Programm durchgeführt wird,<br />

spricht man von einem Semi-Custom ASIC. Ein solcher Entwurf ist oft<br />

signifikant preisgünstiger als ein Full-Custom Entwurf, erreicht aber<br />

nicht die Integrationsdichte eines solchen.<br />

Die folgende Folie zeigt das Bild eines Semi-Custom Chips. Man<br />

erkennt deutlich die Zeilen, in denen die Standardzellen<br />

nebeneinander andgeordnet sind, und zwischen denen sich so<br />

genannte Routing-Kanäle <strong>für</strong> die Verbindung der Standardzellen<br />

untereinander befinden.<br />

Zur Semi-Custom-Klasse zählen auch Gate-Arrays. Dies sind Chips,<br />

bei denen in einem ersten Fabbrikationsschritt eine große Menge von<br />

Gattern auf dem Chip integriert wurde, aber zunächst ohne Routing. In<br />

einem zweiten, vom Kunden gesteuerten Fertigungsprozess, werden<br />

die Verbindungsleitungen entsprechend der kundenspezifischen<br />

Schaltung hinzugefügt. Diese Technologie hat aber in den letzten<br />

Jahren an Bedeutung verloren.<br />

13

Semi-Custom Entwurf<br />

14

Wenn die Strukturen auf dem Silizium weitgehend<br />

anwendungsunspezifisch vorgegeben sind und der Anwender seine<br />

Schaltung durch nachträgliche Manipulation eines solchen Chips<br />

implementiert, spricht man von Field Programmable Logic. Sie wird<br />

also quasi erst im Anwendungsfeld programmiert.<br />

Diese gibt es in zwei grundsätzlich verschiedenen Ausprägungen:<br />

• Einmalig programmierbar<br />

• Reprogrammierbar<br />

Einmalig programmierbare Schaltungen sind in der Regel schneller<br />

und flächeneffizienter aufgebaut. Diese Vorteile stehen dem Nachteil<br />

gegenüber, dass der Entwurfsprozess wesentlich komfortabler mit<br />

reprogrammierbarer Logik gestaltet werden kann. Beispiele da<strong>für</strong><br />

werden wir später kennen lernen.<br />

15

Taxonomie der ICs<br />

Standard ICs<br />

Standard ICs<br />

Logik Logik<br />

Familien<br />

Speicher<br />

Mikroprozessoren<br />

Digitale integrierte Schaltkreise<br />

Digitale integrierte Schaltkreise<br />

Field Fieldpro programmable<br />

Speicher<br />

PROM PROM<br />

EPROM<br />

EEPROM<br />

Logik<br />

Logik<br />

PLDs<br />

PLDs<br />

ASICs<br />

ASICs<br />

Full Full<br />

Custom<br />

Gate- Gate-<br />

Array Array<br />

FPGAs<br />

FPGAs<br />

Semi Semi<br />

Custom<br />

Standard-<br />

Cell Cell<br />

16

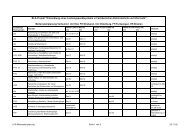

Full-Custom<br />

IC<br />

Standard-<br />

Cell IC<br />

Gate Array FPGA<br />

Anzahl Gatter 500.000.000 10.000.000 1.000.000 1.000.000<br />

Entw.-Zeit 1-2 Jahre 2-4 Monate 3-6 Wochen 1-30 Tage<br />

Entw.-Kosten<br />

Witschaftl.<br />

Stückzahl<br />

hoch<br />

ab ca. 200.000<br />

mittel<br />

ca. 80.000<br />

mittel<br />

ca. 50.000<br />

niedrig<br />

ca. 10.000<br />

ab 100.000 ab 5000 ab 1000 ab 1<br />

PLD<br />

2.000<br />

1 Tag<br />

niedrig<br />

ca. 300<br />

ab 1<br />

17

Rechenleistung<br />

ASIC<br />

Rechenleistung vs. Flexibilität<br />

Spezialrechner<br />

ASIC: application specific integrated circuit<br />

FPGA: field programmable gate array<br />

FPGA<br />

Mikroprozessoren<br />

Größe des<br />

Anwendungsspektrums<br />

18

Integrationsdichte<br />

Höchstintegration vs. schneller Entwurf<br />

ASIC<br />

angepasster<br />

Mikroprozessor<br />

PCB<br />

ASIC: Application Specific Integrated Circuit<br />

FPGA: Field Programmable Gate Array<br />

PLA: Programmable Logic Array<br />

PCB: Printed Circuit Board<br />

PLA<br />

FPGA<br />

Designgeschwindigkeit<br />

19

Typen konfigurierbarer und rekonfigurierbarer Logik<br />

Üblich sind zwei Arten der <strong>Implementierung</strong>:<br />

Schaltnetzrealisierung durch Speicher<br />

Schaltnetzrealisierung mit AND- und OR-Plane<br />

Wir sehen Beispiele <strong>für</strong> die beiden Techniken auf den folgenden<br />

Folien.<br />

Die Realisierung kann unveränderlich oder reprogrammierbar sein. Bei<br />

unveränderlicher Realisierung werden im Moment des Erzeugens der<br />

individuellen Schaltung bestimmte Verbindungen durchtrennt (man<br />

bezeichnet diesen Vorgang häufig als „Brennen“). Die Stellen, an<br />

denen Verbindungen so durchtrennt werden können, werden als<br />

Fuses (Sicherungen) bezeichnet. Durch das Brennen wird die Ein-<br />

Ausgabe-Funktion der Schaltung festgelegt.<br />

Bei reprogrammierbarer Realisierung werden Speicher beschrieben,<br />

die danach den Betrieb der Schaltung steuern. Im Allgemeinen ist der<br />

Speicher selbst schon die Realisierung der Schaltung, d.h. die<br />

Eingaben sind die Adressen und die Ausgaben sind die gespeicherten<br />

Werte.<br />

20

Beispiel: Realisierung eines Schaltnetzes als ROM (Read Only<br />

Memory)<br />

Ein ROM wird zur Generierung des Schaltnetzes mit der Wertetabelle<br />

der zu entwerfenden Funktion beschrieben.<br />

Im Betrieb wird dieses ROM danach benutzt, indem die Eingaben in<br />

das Schaltnetz an die Addresseingänge des ROM gelegt werden, und<br />

die Ausgaben des Schaltnetzes durch die Ausgaben des ROM<br />

geliefert werden.<br />

Eingaben<br />

Ausgaben<br />

21

Beispiel: Ein Volladdierer, realisiert mit einem 8x2-Bit ROM<br />

Wertetabelle ROM<br />

x 2 x 1 x 0 s c<br />

0 0 0 0 0<br />

0 0 1 1 0<br />

0 1 0 1 0<br />

0 1 1 0 1<br />

1 0 0 1 0<br />

1 0 1 0 1<br />

1 1 0 0 1<br />

1 1 1 1 1<br />

Eingaben<br />

x 2 ,x 1 ,x 0<br />

000<br />

001<br />

010<br />

011<br />

100<br />

101<br />

110<br />

111<br />

0 0<br />

1 0<br />

1<br />

0<br />

0 1<br />

1 0<br />

0 1<br />

0 1<br />

1 1<br />

c<br />

s<br />

22

Beispiel: Ein 8x2-Bit ROM (Fuse-Technik, d.h. nicht<br />

reprogrammierbar), bisher noch nicht „gebrannt“<br />

Eingaben<br />

x 2 ,x 1 ,x 0<br />

000<br />

001<br />

010<br />

011<br />

100<br />

101<br />

110<br />

111<br />

1 0 1<br />

1<br />

1<br />

23

Beispiel: Ein Volladdierer, realisiert mit einem 8x2-Bit ROM. Das<br />

„Brennen“ erfolgt durch herausnehmen von Source-Verbindungen der<br />

MOSFETs (Fuses).<br />

1 0 1<br />

Eingaben<br />

x 2 ,x 1 ,x 0<br />

000<br />

001<br />

010<br />

011<br />

100<br />

101<br />

110<br />

111<br />

1<br />

1<br />

s<br />

c<br />

24

Die letzte Folie hat gezeigt: Ein Bit der Wertetabelle einer booleschen<br />

Funktion benötigt in einer Fuse-Technik einen Transistor (der durch<br />

den Prozess des Brennens aktiviert oder deaktiviert sein kann).<br />

Natürlich können wir auch dieselbe Wertetabelle in einem<br />

wiederbeschreibbaren Speicher, z.B. einem SRAM unterbringen. Der<br />

Unterschied ist der Schaltungsaufwand. Für ein Bit in einer SRAM<br />

Zelle benötigen wir 6 Transistoren. D.h. wir haben ungefähr einen um<br />

einen Faktor 6 höheren Flächenaufwand. Entsprechend sind logisch<br />

gleichgroße Speicher in Antifuse-ROM-Technologie kleiner und<br />

schneller.<br />

Dieses Merkmal zieht sich durch alle Schaltkreisfamilien, in denen wir<br />

reprogrammierbare oder einmalig brennbare Bausteine vorfinden. Wir<br />

bezahlen die Reprogrammierbarkeit mit einer geringeren Integrations-<br />

Dichte und einer geringeren Schaltgeschwindigkeit.<br />

25

Der Vorteil von Reprogrammierbarkeit soll aber hier auch nicht<br />

verschwiegen werden: Im Prozess des Entwurfs einer Schaltung ist<br />

die Bearbeitung von Designfehlern und der Test erheblich<br />

kostengünstiger. Dies macht die reprogrammierbaren Bausteine<br />

besonders <strong>für</strong> den Einsatz in Forschung und Entwicklung besonders<br />

attraktiv.<br />

Tatsächlich machen die beiden größten Firmen im Bereich der FPGAs<br />

(Xilinx und Altera) gegenwärtig mehr als 90% ihres Geschäfts mit<br />

reprogrammierbaren Bausteinen.<br />

26

Realisierung eines Schaltnetzes als PLA mit AND- und OR-Plane<br />

AND-Plane<br />

&<br />

&<br />

&<br />

Minterme<br />

OR-plane<br />

≥1 ≥1 ≥1<br />

Eingaben Ausgaben<br />

27

Beispiel: Volladdierer als PLA mit AND- und OR-Plane<br />

x 2<br />

AND-Plane<br />

1 1 1<br />

x 1<br />

x 0<br />

Minterme<br />

OR-plane<br />

s c<br />

28

0<br />

1<br />

0<br />

Beispiel: Funktionen y1 = x0x1x2 + x0x1x2 und y0 = x0x1x2 realisiert als PLA mit AND- und OR-Plane<br />

0<br />

x 2<br />

1 1 1<br />

x 1<br />

x 0<br />

Eingänge Ausgänge<br />

y 1<br />

1<br />

0<br />

y 0<br />

29

FPGA (Field Programmable Gate Arrays)<br />

FPGAs sind heute die leistungsfähigsten anwenderprogrammierbaren<br />

Bausteine. Es gibt weltweit etwa 10 Hersteller, von denen Xilinx, Altera,<br />

Quicklogic, Actel die wichtigsten sind.<br />

Das Konzept des FPGAs ist die Bereitstellung einer Vielzahl von<br />

identischen konfigurierbaren Zellen, so genannten Configurable Logical<br />

Blocks (CLBs). Diese können Boolesche Schaltnetze mit zwischen 4<br />

und 16 Eingängen realisieren und haben in der Regel ein bis vier<br />

Flipflops zur Speicherung der Ergebnisse zur Verfügung.<br />

XilinX: Configurable Logic Block (CLB)<br />

Altera: Logic Element (LE)<br />

Actel: Logic Tile (LT)<br />

QuickLogic: Logic Cell (LC)<br />

In modernen FPGAs wird häufig als zusätzliche Funktionalität ein oder<br />

mehrere Blöcke RAM vorgehalten. Auch das integrieren von einfachen<br />

Prozessorkernen wird unterstützt.<br />

FPGAs gibt es sowohl als einmalig brennbare Bauteile als auch als<br />

reprogrammierbare Einheiten.<br />

Auf der nächsten Folie ist der Floorplan eines typischen FPGAs<br />

abgebildet.<br />

30

Beispiel <strong>für</strong> einen CLB eines XilinX XC3000 FPGAs<br />

31

Beispiel: Floorplan eines FPGA<br />

CLB<br />

RAM<br />

Verdrahtungskanäle<br />

Pad-Cellen <strong>für</strong> die<br />

Verbindung nach außen<br />

32

Ebenen beim Entwurf digitaler Schaltungen<br />

Die Ebenen, die bei dem Entwurf einer Schaltung durchlaufen werden,<br />

definieren die Anforderungen an ein Softwaresystem, das den<br />

Entwurfprozess unterstützen soll. Wir wollen diese Ebenen zunächst<br />

kennen lernen, um danach beurteilen zu können, an welcher Stelle des<br />

Entwurfs wir uns Unterstützung durch Software erhoffen können.<br />

Die oberste Ebene ist die Verhaltensebene. Auf dieser wird die<br />

Schaltung durch Leistungsanforderungen an ihr Ein-Ausgabe-Verhalten<br />

beschrieben. Die Verhaltens-Beschreibung macht keine Festlegung<br />

über die Strukturierung, <strong>Implementierung</strong>, Technologie usw.<br />

Darunter liegt die Architektur-Ebene. Hier wird festgelegt, aus welchen<br />

Komponenten die Schaltung aufgebaut werden soll, mit welchen<br />

Hardware-Bausteinen also die Funktion erfüllt werden kann. Beispiele<br />

<strong>für</strong> solche Bausteine können <strong>für</strong> ein komplexes System wie z.B. das<br />

Motherboard eines Computers die beteiligten Prozessoren,<br />

Speicherchips, Controller, usw. Zwischen diesen Bauteilen bestehen<br />

Schnittstellen, die ebenso wie die Bauteile selbst wiederum funktional<br />

beschrieben werden müssen. Ein Beispiel <strong>für</strong> ein weniger komplexes<br />

33

&<br />

≥1<br />

Abstraktionsebenen beim Entwurf digitaler <strong>Systeme</strong><br />

J Q<br />

K<br />

Verhaltens-Ebene<br />

Architektur-Ebene<br />

RT-Ebene<br />

Logik-Ebene<br />

Transistor-Ebene<br />

Physikalische Ebene<br />

Speicher CPU I/O<br />

A B<br />

Mux<br />

Control<br />

ALU<br />

34

System ist ein zu entwerfender Mikrocontroller. Hier könnten die<br />

Bausteine eine ALU, ein Multiplizierer, ein On-Chip-Cache, ein<br />

Registersatz, eine Befehls-Dekodierungs-Einheit usw. sein. Wiederum<br />

sind diese Komponenten und ihre Schnittstellen funktional zu<br />

beschreiben.<br />

Die Ebene darunter ist die Register-Transfer-Ebene (RT-Ebene).<br />

Bausteine sind hier Register, Multiplexer, Addierer, Schaltnetze, Shifter,<br />

usw. Die Schnittstellen zwischen diesen Einheiten sind Datenpfade, auf<br />

denen Registerinhalte ausgetauscht werden. Das Verhalten der<br />

Einheiten ist durch die Operationen bestimmt, <strong>für</strong> deren Ausführung sie<br />

erforderlich sind.<br />

Unter der Register-Transfer-Ebene liegt die Logik-Ebene. Hier sind die<br />

Einheiten Gatter, Flipflops, Transmissionsgatter. Ihr Verhalten kann<br />

durch boolsche Ausdrücke beschrieben werden.<br />

Unter der Logik-Ebene kommt die Transistor-Ebene. Diese ist aus<br />

Transistoren und passiven Elementen wie Leitungen aufgebaut. Die<br />

physikalischen Ebenen unterhalb der Transistor-Ebene sollen uns in<br />

dieser Vorlesung nicht interessieren.<br />

35

Verhaltens-<br />

Ebene<br />

Architektur<br />

Ebene<br />

Register Transfer<br />

Ebene<br />

Verhaltensbeschreibung<br />

Struktur<br />

Leistungsanforderungen keine<br />

Ein-Ausgabeverhalten<br />

der Architektur<br />

Datenfluss, State<br />

Machines<br />

Blockschaltbild<br />

RT-Diagramme<br />

Logik-Ebene Boolesche Gleichungen Netzliste<br />

Transistor-Ebene Differenzialgleichungen el. Schaltbild<br />

Elemente<br />

Prozessoren, Speicher<br />

Busse, Controller<br />

Register, Multiplexer,<br />

Dekodierer<br />

Flipflops, Gatter<br />

Transistoren, Dioden<br />

Kondensatoren<br />

36

Daten<br />

Speicher<br />

Befehls-Dekodierung<br />

ALU<br />

FPU<br />

Multiplizierer<br />

Daten, Befehle, Selektoren<br />

OP-<br />

Muxe<br />

Clk<br />

Daten<br />

Daten, Befehle, Selektoren<br />

37

Spaltenselektor<br />

In<br />

Zeilenselektor<br />

In<br />

Datalink<br />

Westen<br />

Vom CW<br />

Spaltenselektor<br />

Out<br />

2<br />

12<br />

2<br />

Instruction<br />

Out<br />

Instruction<br />

In<br />

rs cs<br />

Writeport<br />

ALU<br />

6<br />

Datalink<br />

Norden<br />

Flag-Manager<br />

Floating Point Einheit (FPU)<br />

Shifter<br />

Datalink<br />

Süden<br />

RAM-Registerfile<br />

Befehlsdekoder<br />

Bedingt-Logische<br />

Einheit<br />

Multipizierer<br />

Vom CN<br />

R0<br />

R1<br />

R31<br />

Op0-Indexreg. Op1-Indexreg. Res-Indexreg.<br />

Kommunikationsregister<br />

Vom CS<br />

Op0-MUX<br />

Read-<br />

Port<br />

Op1-MUX<br />

Clock-<br />

Verteiler<br />

Zeilenselektor<br />

Out<br />

Datalink<br />

Osten<br />

Vom CE<br />

Clock<br />

38

ybar<br />

x<br />

r_mult<br />

s_mult<br />

1<br />

≥1<br />

VA<br />

≥1<br />

VA<br />

39

Beim Entwurf eines digitalen Systems durchläuft man die hier<br />

angesprochenen Ebenen der Abstraktion.<br />

In bestimmten Entwurfsprozessen ist die Detailkenntnis aller Ebenen<br />

nicht erforderlich. Z.B. braucht ein Standard-Cell-Designer nur sehr<br />

wenig über die Transistor-Ebene zu wissen, da sein Entwurfziel auf der<br />

Logik-Ebene bereits erreicht ist. Die Umsetzung seiner bis dahin<br />

entworfenen Schaltung in ein physikalisches Layout ist Aufgabe des<br />

Semi-Custom-Entwurfssystems (also eines Programms).<br />

Wir favorisieren hier einen Top-Down-Entwurfsprozess. Wir wollen bei<br />

unseren Entwürfen bei der Verhaltens-Ebene beginnen, und nach und<br />

nach auf dem Weg hinunter zur Logik-Ebene das Verhalten der<br />

Schaltung durch eine Strukturierung ihrer Bauteile sicherstellen. Man<br />

implementiert also auf diesem Weg „Verhalten“ durch „Struktur“.<br />

Begleitend soll der Entwurf in jeder Phase überprüfbar korrekt sein. Dies<br />

geschieht durch Simulation.<br />

43

Simulation erfordert die Modellierung der<br />

Schaltung auf der jeweiligen<br />

Entwurfsebene und die Kontrolle der<br />

Funktion dieses Modells bei der Eingabe<br />

von aussagefähigen Simulationsstimuli<br />

(Eingabewerten).<br />

44

Am wünschenswertesten ist eine Simulationsumgebung, die unabhängig<br />

vom Stadium des Entwurfs (dem Anteil von Verhaltensmodell und<br />

Strukturmodell) ist. Man möchte also einen Satz von Simulationsstimuli<br />

benutzen, mit dem dieselbe Funktionalität in allen Ebenen des Entwurfs<br />

verifiziert werden kann.<br />

45

Strukturelle vs. Verhaltensbeschreibung von Schaltungen<br />

Man kann Schaltungen mit Ihrer Struktur oder mit ihrem Verhalten<br />

beschreiben. Bei der Beschreibung mittels der Struktur beziehen wir uns<br />

auf den Aufbau der Schaltung aus einzelnen Komponenten, die<br />

wiederum ihrerseits beschrieben werden können. Bei einer<br />

Verhaltensbeschreibung wird angegeben, welche datenverarbeitenden<br />

Prozesse die Schaltung realisiert. Wir beschreiben also ihr<br />

Verarbeitungsverhalten der Eingangsdaten und geben auf diese Weise<br />

algorithmisch an, wie die Ausgangsdaten aus den Eingangsdaten<br />

berechnet werden.<br />

Man kann Strukturbeschreibung und Verhaltensbeschreibung mischen.<br />

Z.B. könnten die Komponenten einer Strukturbeschreibung eines<br />

Bausteins in ihrem Verhalten beschrieben werden. Im Hardwareentwurf<br />

beginnen wir in der Regel mit Verhaltensbeschreibungen. Diese werden<br />

dann nach und nach durch Strukturbeschreibungen ersetzt.<br />

Der Prozess des Hardwareentwurfs kann also im weitesten Sinne als<br />

kontinuierliche Ersetzung von Verhalten durch Struktur verstanden<br />

werden.<br />

46

Definition<br />

Unter einer strukturellen Beschreibung eines Bausteins versteht man<br />

die Beschreibung einer Skizze, die angibt, welche Komponenten (und<br />

wie viele Instanzen der Komponenten) zur Realisierung des Bausteins<br />

genutzt werden und wie diese Komponenten mit den Ein- und<br />

Ausgängen des Bausteins verdrahtet sind.<br />

47

Definition<br />

Unter einer Verhaltensbeschreibung eines Bausteins versteht die<br />

funktionale Modellierung seines Ein-/Ausgabeverhaltens.<br />

48

Beispiel: Verhaltensbeschreibung eines Volladdierers<br />

architecture Behavioral of VA is<br />

Begin<br />

s

Beispiel: Strukturbeschreibung eines Volladdierers<br />

architecture Structural of VA is<br />

BEGIN<br />

HA1: HA PORT MAP(<br />

A => A,<br />

B => B,<br />

S => S1HA,<br />

Cout => C1HA<br />

);<br />

HA2: HA PORT MAP(<br />

A => S1HA,<br />

B => Cin,<br />

S => S2HA,<br />

Cout => C2HA<br />

);<br />

Cout

Beispiel: Der FPGA-Entwurfsablauf ab der RT-Ebene<br />

Eingabe<br />

VHDL Verilog<br />

Netzliste<br />

Synthese<br />

Implementation<br />

Bitfile<br />

Chip<br />

Programmierung<br />

Verhaltenssimulation<br />

Funktionale Simulation<br />

Statische Timing Analyse<br />

Timing Simulation<br />

In-Circuit Verification<br />

Verifikation<br />

51

Synthese<br />

VHDL<br />

VHDL<br />

Syntax Check<br />

grafische RTL<br />

Darstellung<br />

Technology Mapping<br />

Netzliste<br />

Netzliste<br />

Netzliste<br />

Überprüfung des VHDL Codes<br />

auf Syntax und Semantik<br />

Abbildung der Logik von RTL<br />

Ebene auf Gatter-Ebene<br />

52

Implementation<br />

Netzliste<br />

Netzliste<br />

Netzliste<br />

Translate<br />

Map<br />

Place & Route (PAR)<br />

Bitfile<br />

Constraints<br />

Generiert aus mehreren Netzlisten und<br />

Constraints eine einzige Netzliste<br />

Logischer „Design Rule Check“ und<br />

Abbildung der Logik auf<br />

Komponententypen der Zielarchitektur<br />

Abbildung der Komponenten auf<br />

definierte physikalische Einheiten der<br />

Zielarchitektur und erstellen<br />

der Verbindungen<br />

53

Funktion der Hardwarebeschreibungssprache<br />

Die Hardware Description Language (HDL) hat die Aufgabe, den<br />

Entstehungsprozess eines Hardwareentwurfs durch die verschiedenen<br />

Ebenen zu unterstützen. Die Sprachen Verilog HDL und VHLD sind<br />

weltweit etwa gleichstark vertreten. In Europa gibt es ein Übergewicht<br />

von VHDL, in Amerika von Verilog HDL.<br />

HDLs unterstützen den Top-Down-Entwurf. In der HDL kann eine<br />

Schaltung auf der Verhaltensebene modelliert und simuliert werden.<br />

Sodann kann sie durch schrittweise Ersetzung von Verhalten durch<br />

Struktur in eine synthetisierbare Form gebracht werden. Jeder dieser<br />

Schritte kann wiederum durch Simulation verifiziert werden.<br />

Die finale strukturierte HDL-Beschreibung ist schließlich die Eingabe in<br />

das zur Verfügung stehende Synthese-Tool.<br />

Gegenstand dieser Vorlesung ist das Erlernen von VHDL in der<br />

Anwendung, einfache Schaltungen auf eine FPGA-Zielarchitektur zu<br />

bringen.<br />

54

Funktion der Hardwarebeschreibungssprache<br />

• Macht die Komplexität heutiger <strong>Systeme</strong> beherrschbar<br />

• Manueller Entwurf fehleranfällig<br />

• Simulation des Gesamtsystems zu rechenaufwendig<br />

• Entwurfsaufgaben können auf meherere Personen verteilt werden<br />

• Wiederverwendung von bestehenden Entwürfen wird unterstützt<br />

• Kann zum Datenaustausch dienen<br />

• Auftraggeber und –nehmer<br />

• Entwickler im selben Entwurfsteam<br />

• Zwischen verschiedenen Ebenen des Entwurfs<br />

• Zwischen unterschiedlichen Tools verschiedener Hersteller<br />

• Kann der Dokumentation dienen<br />

• Lebensdauer des Systems höher als Zugriffszeit auf Entwickler<br />

• Erleichtert Wiederverwendung bei Modifikationen im Entwurf<br />

• Erleichtert Wiederverwendung bei Technologiewechsel<br />

• Garantiert Konsistenz in der Dolumentation<br />

55