Grundlagen der Informatik III Wintersemester 2010/2011 â 28 ...

Grundlagen der Informatik III Wintersemester 2010/2011 â 28 ...

Grundlagen der Informatik III Wintersemester 2010/2011 â 28 ...

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

<strong>Grundlagen</strong> <strong>der</strong> <strong>Informatik</strong> <strong>III</strong><br />

<strong>Wintersemester</strong> <strong>2010</strong>/<strong>2011</strong> – <strong>28</strong>. Vorlesung<br />

Dr.-Ing. Wolfgang Heenes<br />

int main() {<br />

printf("Hello, world!");<br />

return 0;<br />

}<br />

msg:<br />

main:<br />

.data<br />

.asciiz "Hello, world!"<br />

.text<br />

.globl main<br />

la $a0,msg<br />

li $v0,4<br />

syscall<br />

jr $ra<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 1

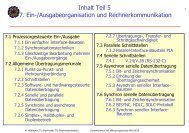

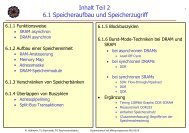

Inhalt<br />

1. Literatur<br />

2. Multiprozessorsysteme<br />

3. Verbindungsnetzwerke<br />

4. Kostenmodelle und Kommunikationsmodelle<br />

5. Anwendung von Verbindungsnetzwerken<br />

6. Praktische Realisierungen<br />

7. Zusammenfassung und Ausblick<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 2

Literatur<br />

[Sch97] Schürmann, Bernd: Rechnerverbindungsstrukturen.<br />

Vieweg Verlag, Braunschweig, Wiesbaden, 1997.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 3

Multiprozessorsysteme<br />

◮ Multiprozessorsysteme werden nach Flynn´s Taxonomie in die Klasse MIMD<br />

eingeteilt.<br />

◮ Anhand <strong>der</strong> Entfernung <strong>der</strong> Systemkomponenten und <strong>der</strong> Übertragungsrate<br />

wird festgelegt, ob ein paralleles Rechnersystem als Multiprozessorsystem<br />

bezeichnet wird<br />

◮ Taxonomie: Multiprozessorsysteme werden auf einer ersten Ebene in<br />

speichergekoppelte und nachrichtengekoppelte Systeme unterteilt.<br />

◮ In <strong>der</strong> Vergangenheit wurden verschiedene Multiprozessorsysteme mit<br />

mehrstufigen Schalternetzwerken gebaut.<br />

◮ Ein nachrichtengekoppeltes Multiprozessorsystem ist <strong>der</strong><br />

SUPRENUM-1-Rechner<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 4

Multiprozessorsysteme<br />

◮ Die Abbildung zeigt ein Rechnersystem mit physikalisch gemeinsamem<br />

Speicher.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 5

Multiprozessorsysteme<br />

◮ Die physikalische Struktur eines Rechnersystems mit verteiltem Speicher ist<br />

in <strong>der</strong> folgenden Abbildung zu sehen. Je<strong>der</strong> Knoten besteht aus einem<br />

Prozessor und einem Speicher und ggf. <strong>der</strong> I/O Peripherie. Die Knoten<br />

werden über ein Verbindungsnetzwerk gekoppelt.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 6

Verbindungsnetzwerke<br />

◮ Die Verbindungsnetzwerke sind ein wesentlicher Bestandteil von<br />

Parallelrechnern und bestimmen maßgeblich <strong>der</strong>en Leistungsfähigkeit [Sch97]<br />

◮ Ein Verbindungsnetzwerk ist innerhalb eines Parallelrechners in zwei<br />

Ausprägungen vorhanden.<br />

◮ Verbindungsnetzwerk zur Kopplung von Prozessoren, Speichern und<br />

I/O-Einheiten<br />

◮ Verbindungsnetzwerk zur Kopplung mehrerer Knoten, wobei je<strong>der</strong> Knoten aus<br />

Prozessor, Speicher und I/O-Einheiten besteht<br />

◮ Verbindungsnetzwerke sind auch in <strong>der</strong> Kommunikationstechnik (Telefon) zu<br />

finden.<br />

◮ Nach was für Kriterien werden Verbindungsnetzwerke charakterisiert?<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 7

Verbindungsnetzwerke<br />

◮ Die Kriterien, nach denen Verbindungsnetzwerke charakterisiert werden, sind:<br />

◮ Die Übertragungsgeschwindigkeit/Bandbreite des Verbindungsnetzwerks.<br />

Außerdem ist die Bisektionsbandbreite, also die Bandbreite die benötigt wird,<br />

wenn die eine Hälfte <strong>der</strong> Knoten an die an<strong>der</strong>e Hälfte gleichzeitig sendet, eine<br />

wichtige Kenngröße.<br />

◮ Die Latenz des Verbindungsnetzwerks. Damit wird die Verzögerung<br />

beschrieben, die vom Absenden einer Nachricht bzw. eines Datums bis zur<br />

Ankunft und <strong>der</strong> Verarbeitung gemessen wird.<br />

◮ Skalierbarkeit bezeichnet die Eigenschaft, ein Verbindungsnetzwerk (modular)<br />

zu erweitern.<br />

◮ Das Blockierungsverhalten beschreibt, inwiefern ggf. Einschränkungen auf<br />

bestehende Verbindungen durch an<strong>der</strong>e Verbindungen zu erwarten sind.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 8

Verbindungsnetzwerke<br />

◮ Weitere Kriterien an ein Verbindungsnetzwerk sind die Kosten, die räumliche<br />

Ausdehnung und die Fehlertoleranz.<br />

◮ Die Einteilung <strong>der</strong> Verbindungsnetzwerke kann nach folgenden Kriterien<br />

vorgenommen werden.<br />

◮ Topologie<br />

◮ Verbindungsart<br />

◮ Steuerung des Verbindungsaufbaus<br />

◮ Arbeitsweise<br />

◮ Die Topologie spielt dabei eine herausragende Rolle, da sie Eigenschaften<br />

wie Skalierbarkeit entscheidend mitbestimmt.<br />

◮ Die Auswahl des geeigneten Verbindungsnetzwerks trägt im Wesentlichen zur<br />

Leistungssteigerung eines Parallelrechners bei, da in <strong>der</strong> Regel die<br />

Leistungsgrenze immer durch die erzielbare Speicherbandbreite und die<br />

Kommunikationsbandbreite begrenzt ist.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 9

Verbindungsnetzwerke<br />

◮ Die Topologie, also die räumliche Anordnung eines Verbindungsnetzwerkes,<br />

kann in reguläre und irreguläre Strukturen unterteilt werden.<br />

◮ Irreguläre Strukturen werden in Parallelrechnern selten eingesetzt.<br />

◮ Reguläre Strukturen haben den Vorteil, Prozessoren und damit auch auf das<br />

Programmiermodell bezogen Prozesse in regelmäßigen Strukturen<br />

anzuordnen.<br />

◮ Des Weiteren unterscheidet man statische und dynamische<br />

Verbindungsnetzwerke.<br />

◮ Statische Netzwerke sind feste Punkt zu Punkt Verbindungen <strong>der</strong> Prozessoren<br />

◮ dynamische Netzwerke enthalten Schaltelemente, die durch<br />

Konfigurationsinformationen eine bestimmte Verbindung herstellen können<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 10

Statische Verbindungsnetzwerke<br />

◮ Bei <strong>der</strong> Einführung <strong>der</strong> Zellularen Automaten wurden bereits zwei<br />

Verbindungsnetzwerke beschrieben, nämlich das zweidimensionale und das<br />

hexagonale Gitter.<br />

◮ In Verbindungsnetzwerken werden solche Gitter häufig zur Lösung<br />

zweidimensionaler Probleme eingesetzt.<br />

◮ Der Vorteil ist die feste Anzahl von vier Verbindungskanälen (Links) bei<br />

beliebiger Größe des Gitters.<br />

◮ Um die Kommunikation an den Rän<strong>der</strong>n des Gitters nicht abbrechen zu<br />

lassen, kann das Gitter zum Torus geschlossen werden.<br />

◮ Im Prinzip beliebige Geometrien möglich<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 11

Statische Verbindungsnetzwerke<br />

◮ Wichtige statische Topologien sind<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 12

Statische Verbindungsnetzwerke<br />

◮ Die vollständige Vernetzung 1 verbindet alle Knoten mit je einem Link<br />

untereinan<strong>der</strong> und stellt damit die verbindungsreichste Topologie dar.<br />

◮ Der Aufwand von N − 1 Kommunikationskanälen pro Knoten ist allerdings nur<br />

für relativ kleine N möglich.<br />

◮ Deswegen wird in vielen Parallelrechnern die vollständige Vernetzung nicht<br />

verwendet, obwohl die Eigenschaften, nur einen Verbindungsschritt (hop) zu<br />

benötigen und keine Resourcenkonflikte zu verursachen, bei <strong>der</strong> Realisierung<br />

von Parallelrechnern ideal sind.<br />

1 engl.: completely interconnected<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 13

Dynamische Verbindungsnetzwerke<br />

◮ Dynamische Verbindungsnetzwerke enthalten konfigurierbare Schaltelemente<br />

und werden in einstufige und mehrstufige Netze eingeteilt.<br />

◮ Zu den einstufigen, dynamischen Verbindungsnetzwerken gehören das<br />

Shuffle-Netzwerk, <strong>der</strong> Crossbar und <strong>der</strong> Bus.<br />

◮ Mehrstufige dynamische Verbindungsnetzwerke werden oft aus einstufigen<br />

Elementen zusammengesetzt.<br />

◮ Die Struktur <strong>der</strong> Verbindungen bezeichnet dann das Netzwerk (Butterfly,<br />

Omega usw.)<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 14

Dynamische Verbindungsnetzwerke<br />

◮ Der Crossbar o<strong>der</strong> Kreuzschienenverteiler ist das universellste dynamische<br />

Verbindungsnetz. Es gestattet mit nur einer Stufe, beliebige Paare von Einund<br />

Ausgängen miteinan<strong>der</strong> zu verbinden. Außerdem ist es möglich, an alle<br />

Empfänger eine Nachricht zu senden (broadcast). Die Abbildung zeigt einen<br />

2×2 Crossbar.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 15

Dynamische Verbindungsnetzwerke<br />

◮ Die Schalter einer Zeile (z. B. K12 und K22) dürfen nicht gleichzeitig aktiviert<br />

werden.<br />

◮ Schließlich kann an E1 eine logische Null und an E2 eine logische Eins<br />

anliegen.<br />

◮ Aus diesem Grund besitzen Crossbars sogenannte Arbitrierungseinheiten.<br />

◮ Die Komplexität <strong>der</strong> Schaltung mit n Eingängen und n Ausgängen ist O(n 2 ).<br />

◮ Zusätzlich ist allerdings noch die Logik für die Arbitrierungseinheiten zu<br />

berücksichtigen.<br />

◮ Ein dynamisches Verbindungsnetzwerk mit sehr großer Verbreitung ist <strong>der</strong><br />

Bus.<br />

◮ Der Bus ist ein Crossbar mit <strong>der</strong> Konfiguration m×1 und damit eine Spalte<br />

dieses Verbindungsnetzwerkes.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 16

Dynamische Verbindungsnetzwerke<br />

◮ Bus (Fortsetzung)<br />

◮ Er ist kostengünstig realisierbar.<br />

◮ Allerdings ist die Bandbreite begrenzt und skaliert nicht.<br />

◮ Die Latenzzeiten sind höher und auch das Blockierungsverhalten wesentlich<br />

kritischer als beim Crossbar.<br />

◮ In Parallelrechnern wird <strong>der</strong> Bus deswegen nur zur Steuerung von peripheren<br />

Komponenten verwendet<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 17

Dynamische Verbindungsnetzwerke<br />

◮ Das Shuffle-Netzwerk lässt sich ebenfalls aus <strong>der</strong> Crossbar-Struktur ableiten.<br />

◮ Abbildung zeigt die Schaltfunktionen.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 18

Dynamische Verbindungsnetzwerke<br />

◮ Ist K unwahr, so erfolgt die Verbindung von E1 nach A1 und von E2 nach A2<br />

◮ Ist K wahr, so vertauscht sich die Zuordnung <strong>der</strong> Ausgänge<br />

◮ Einige Ausprägungen des Shuffle-Netzwerks sind um eine Broadcastfunktion<br />

erweitert worden<br />

◮ Das Shuffle-Netzwerk ist durch die eingeschränkte Struktur nicht mehr<br />

skalierbar.<br />

◮ Viele mehrstufige Verbindungsnetzwerke sind aus dem Schaltelement des<br />

Shuffle-Netzwerks zusammengesetzt.<br />

◮ Zu den mehrstufigen Verbindungsnetzwerken gehören das Omega-Netz und<br />

das Butterfly-Netz.<br />

◮ Darstellung verschiedener Permutationsnetzwerke (Exchange,<br />

Perfect-Shuffle, Butterfly, Bit reversed)<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 19

Dynamische Verbindungsnetzwerke<br />

Butterfly-Netzwerk<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 20

Dynamische Verbindungsnetzwerke<br />

◮ Neben <strong>der</strong> Topologie trägt die Verbindungsart einen großen Teil zur<br />

Leistungsfähigkeit eines Verbindungsnetzes bei.<br />

◮ Bei den dynamischen Verbindungsnetzwerken wird die Leitungsvermittlung<br />

und die Paketvermittlung unterschieden.<br />

◮ Die Leitungsvermittlung ist eine physikalische Verbindung und erfor<strong>der</strong>t einen<br />

Leitungsaufbau, die Übertragung <strong>der</strong> Daten und einen Leitungsabbau.<br />

◮ Die Paketvermittlung übergibt einen Datenblock (Paket) an das<br />

Verbindungsnetz, welches das Paket über wechselnde Routen zum Ziel<br />

transportiert.<br />

◮ Der Vorteil <strong>der</strong> Paketvermittlung ist, dass Ressourcen nur belegt werden,<br />

wenn diese auch benötigt werden und eine alternative Wegewahl möglich ist.<br />

◮ Der Nachteil gegenüber <strong>der</strong> Leitungsvermittlung ist, dass die Zeit für die<br />

Übertragung proportional zur Anzahl <strong>der</strong> Verbindungsschritte ist.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 21

Bulk-Synchronous Parallel Modell I<br />

◮ Das Bulk-Synchronous Parallel Modell (BSP) ist ein nachrichtengekoppeltes<br />

Modell<br />

◮ Es erlaubt den Prozessoren eine asynchrone Arbeitsweise und modelliert<br />

Latenzeit und begrenzte Bandbreite<br />

◮ Ein mit dem BSP Modell beschriebener Rechner besteht: aus einer Menge<br />

von Prozessoren (es ist dabei unerheblich, ob die Prozessoren lokalen<br />

Speicher besitzen).<br />

◮ einem Kommunikationsnetz für das Verschicken von Nachrichten und einem<br />

Mechanismus für die Barrieren-Synchronisation.<br />

◮ Eine Berechnung enthält eine Sequenz sogenannter Superschritte. Ein<br />

Superschritt besteht aus einer Anzahl von lokalen Berechnungsschritten und<br />

<strong>der</strong> Nachrichtenübertragungen, also dem Senden und Empfangen von<br />

Nachrichten an bzw. von an<strong>der</strong>en Komponenten.<br />

◮ Danach wird eine Barrierensynchronisation aller Prozessoren durchgeführt,<br />

bevor <strong>der</strong> nächste Superschritt starten kann.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 22

Bulk-Synchronous Parallel Modell II<br />

◮ Durch das Einführen <strong>der</strong> Superschritte werden Kommunikation und<br />

Synchronisation voneinan<strong>der</strong> entkoppelt.<br />

◮ Außerdem werden Verklemmungen durch race conditions vermieden.<br />

◮ Der globale Zustand <strong>der</strong> Programmausführung ist bei <strong>der</strong> Ausführung <strong>der</strong><br />

Barriere am Ende eines Superschrittes bekannt.<br />

◮ Das BSP Modell ist durch folgende drei Attribute definiert.<br />

◮ Die Anzahl p <strong>der</strong> Komponenten mit Berechnungs- und/o<strong>der</strong> Speicherfunktion<br />

(Prozessoren).<br />

◮ Einen Faktor g, <strong>der</strong> Kommunikationskosten in Berechnungskosten überführt.<br />

◮ Die minimale Zeit L zwischen zwei Synchronisationen. Diese Zeit ist auch als Zeit<br />

für die Ausführung eines Superschritts zu interpretieren.<br />

◮ Eine technische Realisierung des BSP Modells ist, abgesehen von <strong>der</strong><br />

Barrierensynchronisation, in nachrichtengekoppelten<br />

Multiprozessorarchitekturen zu finden.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 23

LogP<br />

◮ Ein Modell zur Beurteilung <strong>der</strong> Verbindungskosten ist das LogP Modell.<br />

◮ Der Austausch <strong>der</strong> Daten zwischen den Prozessoren wird durch Nachrichten<br />

realisiert.<br />

◮ Das LogP Modell definiert also ein nachrichtengekoppeltes Maschinenmodell.<br />

◮ Dieses Modell abstrahiert von <strong>der</strong> Struktur und den Eigenschaften des<br />

Verbindungsnetzwerks, Konflikte im Verbindungsnetz werden nicht<br />

berücksichtigt.<br />

◮ Vier charakteristische Parameter L, o, g und P werden definiert:<br />

◮ Die Latenzzeit L (latency) ist die maximal benötigte Zeit für die Übertragung einer<br />

kleinen Nachricht.<br />

◮ Der Aufwand o (overhead) beschreibt die Zeitdauer für den Sende- bzw.<br />

Empfangsvorgang.<br />

◮ Mit g (gap) wird das kleinste Zeitintervall bezeichnet, welches zwischen <strong>der</strong><br />

Übertragung von zwei Nachrichten eingehalten werden muss.<br />

◮ Die Anzahl <strong>der</strong> Prozessor- und/o<strong>der</strong> Speichermodule P. Die Zeiteinheit für eine<br />

Operation wird als Zyklus bezeichnet. Die Parameter L, o und g werden als<br />

Vielfache des Zyklus gemessen bzw. angegeben.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 24

Anwendung von Verbindungsnetzwerken<br />

◮ Verbindung von mehreren Prozessoren<br />

◮ Anwendungen müssen Parallelität unterstützen<br />

◮ Parallele Algorithmen<br />

◮ Vielzahl von Algorithmen, die für spezielle Architekturen<br />

(Verbindungsstrukturen) entwickelt wurden.<br />

◮ Parallele Algorithmen sind für<br />

◮ Sortieren<br />

◮ Matrixmultiplikation<br />

◮ Graphenalgorithmen<br />

◮ ...<br />

entwickelt worden.<br />

◮ Hier das einfache Beispiel des Bitonischen Mischens<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 25

Bitonisches Mischen<br />

◮ Gegeben ist eine Bitonische Folge:<br />

◮ 1, 7, 9, 12, 13, 11, 8, 2<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 26

Anwendung von Verbindungsnetzwerken<br />

◮ Analyse: Jede Zelle (Prozessor) enthält ein Datum<br />

◮ Auszuführende Operation: Vergleich <strong>der</strong> Daten, die in <strong>der</strong> Zelle gespeichert<br />

sind<br />

◮ ggf. Austausch<br />

◮ Wichtig: Synchronisation aller Prozessoren am Schluss, damit es nicht zu<br />

Inkonsistenzen kommt<br />

◮ Implementierung mit Prozessen (Threads)?!<br />

◮ Aufwand: Kommunikationskosten vs. Berechnungskosten (Vergleich)<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 27

Bitonisches Sortieren<br />

◮ Gegeben ist eine beliebige Folge:<br />

◮ 7, 12, 1, 5, 13, 1, 4, 3<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | <strong>28</strong>

Anwendung von Verbindungsnetzwerken<br />

◮ Analyse: Nach dem Erzeugen <strong>der</strong> Bitonischen Folge erfolgt das Mischen<br />

◮ Realisierung <strong>der</strong> Kommunikation über Verbindungsnetzwerk<br />

◮ In diesem Fall z. B. Omega-Netzwerk<br />

◮ Verbindungsstruktur<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 29

Bitonisches Sortieren<br />

◮ Erster Schritt<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 30

Bitonisches Sortieren<br />

◮ Zweiter Schritt<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 31

Bitonisches Sortieren<br />

◮ Dritter Schritt<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 32

Blockmatrixzerlegung<br />

◮ Gegeben ist eine Matrix<br />

A =<br />

⎛<br />

⎜<br />

⎝<br />

⎞<br />

a 00 a 01 a 02 a 03<br />

a 10 a 11 a 12 a 13<br />

⎟<br />

a 20 a 21 a 22 a 23<br />

⎠<br />

a 30 a 31 a 32 a 33<br />

◮ Zerlegung<br />

( )<br />

a00 a<br />

A 00 =<br />

01<br />

a 10 a 11<br />

A 01 =<br />

( )<br />

a02 a 03<br />

a 12 a 13<br />

A 10 =<br />

( )<br />

a20 a 21<br />

a 30 a 31<br />

A 11 =<br />

( )<br />

a22 a 23<br />

a 32 a 33<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 33

Blockmatrixzerlegung<br />

◮ Mit analogen Definitionen für die Matrizen B und C kann die<br />

Matrixmultiplikation wie folgt dargestellt werden:<br />

( ) ( )<br />

A00 A<br />

C = A·B =<br />

01 B00 B<br />

·<br />

01<br />

A 10 A 11 B 10 B 11<br />

=<br />

=<br />

=<br />

( )<br />

A00 · B 00 + A 01 · B 10 A 00 · B 01 + A 01 · B 11<br />

A 10 · B 00 + A 11 · B 10 A 10 · B 01 + A 11 · B 11<br />

( ) ( )<br />

A00 · B 00 A 00 · B 01 A01 · B<br />

+<br />

10 A 01 · B 11<br />

A 10 · B 00 A 10 · B 01 A 11 · B 10 A 11 · B 11<br />

( )<br />

C00 C 01<br />

C 10 C 11<br />

◮ Die vier Ergebnisblockmatrizen C 00 bis C 11 können unabhängig voneinan<strong>der</strong><br />

berechnet werden.<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 34

Blockmatrixzerlegung<br />

◮ Auf einem CC-Modell (Connected Cube)<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 35

Praktische Realisierungen<br />

einer Multiprozessorarchitektur<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 36

Altera - NIOS II<br />

◮ 32 General Purpose Register<br />

Nios II Processor Core<br />

Tightly Coupled<br />

JTAG<br />

interface<br />

to software<br />

debugger<br />

reset<br />

clock<br />

cpu_resetrequest<br />

cpu_resettaken<br />

JTAG<br />

Debug Module<br />

Program<br />

Controller<br />

&<br />

Address<br />

Generation<br />

Exception<br />

General<br />

Purpose<br />

Registers<br />

Control<br />

Registers<br />

Instruction<br />

Cache<br />

Instruction Memory<br />

Tightly Coupled<br />

Instruction Memory<br />

Instruction Bus<br />

Controller<br />

irq[31..0]<br />

Interrupt<br />

Controller<br />

Instruction<br />

Regions<br />

Memory<br />

Memory<br />

Management<br />

Unit<br />

Protection<br />

Unit<br />

Translation<br />

Data<br />

Regions<br />

Lookaside<br />

Buffer<br />

Data Bus<br />

Custom<br />

I/O<br />

Signals<br />

Custom<br />

Instruction<br />

Logic<br />

Arithmetic<br />

Logic Unit<br />

Data<br />

Cache<br />

Tightly Coupled<br />

Data Memory<br />

Tightly Coupled<br />

Data Memory<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 37

Realisierung <strong>der</strong> Architektur auf FPGA<br />

◮ Kenngrößen<br />

- A B C D E F G H I J K<br />

p total total ALUTs ALUTs network network registers memory register max. max. DMIPS<br />

ALMs ALUTs for for per over for bits bits clock DMIPS speed<br />

processors network processor processor ALUTs network (MHz) up<br />

1 1,203 1,592 1,592 - - - - 195,296 1,520 200 232 1.0<br />

4 4,355 5,437 4,683 326 81.50 6.9% 184 <strong>28</strong>9,568 4,995 133 617 2.6<br />

8 8,344 10,780 9,006 922 115.25 10.2% 368 415,264 9,568 120 1113 4.8<br />

16 17,638 21,935 17,697 2,616 163.50 14.8% 736 666,656 18,726 95 1763 7.6<br />

32 36,577 44,441 34,404 6,637 207.40 19.3% 1,472 1,169,440 37,047 75 2784 12.0<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 38

Realisierung <strong>der</strong> Architektur auf FPGA<br />

◮ Anwendung, Sortieren von Zahlen: Algorithmen ⇒ Quicksort, Bitonic Sort<br />

processors cycles cycle speed-up execution time real speed-up<br />

1 4,971,726 1.00 24.8 ms 1.0<br />

4 1,443,694 3.4 10.8 ms 2.3<br />

8 726,336 6.8 6.0 ms 4.1<br />

16 366,650 13.5 3.8 ms 6.4<br />

32 182,598 27.2 2.4 ms 10.2<br />

sorted data random data<br />

algorithm cycles execution time cycles execution time<br />

standard quicksort 23,314,342 169.56 ms 502,411 3.65 ms<br />

median quicksort 420,197 3.06 ms 542,098 3.94 ms<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 39

Zusammenfassung und Ausblick<br />

◮ Multiprozessorsysteme<br />

◮ Verbindungsnetzwerke<br />

Nächste Vorlesung behandelt<br />

◮ Kommunikationsnetze<br />

9. Februar <strong>2011</strong> | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 40