Einführung in Computer Microsystems

Einführung in Computer Microsystems

Einführung in Computer Microsystems

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Prof. Dr.-Ing. Sor<strong>in</strong> A. Huss<br />

E<strong>in</strong>führung <strong>in</strong><br />

<strong>Computer</strong> <strong>Microsystems</strong><br />

Sommersemester 2009<br />

FSL_V20 Register Descriptions<br />

Lösungsvorschlag<br />

Not applicable.<br />

11<br />

Fast SImplex L<strong>in</strong>k (FSL) Bus (v2.11a)<br />

Unter http://www.vlsi.<strong>in</strong>formatik.tu-darmstadt.de/student_area/kv_CompMicroSys/ f<strong>in</strong>den Sie den zur Übung<br />

11 aktuellen VHDL-Quellcode, der die modulare Addition und Montgomery-Multiplikation implementiert.<br />

FSL_V20 Interrupt Descriptions<br />

FSL-Anb<strong>in</strong>dungFür The signals FSL_Has_Data, die modulare Addition FSL_Full und and dieFSL_Control_IRQ Montgomery-Multiplikation have <strong>in</strong>terrupt soll e<strong>in</strong> properties Interface anthat den FSL make (Fast them Simplex<br />

L<strong>in</strong>k) erstellt werden. Der E<strong>in</strong>fachheit halber soll die Komponente nur Daten empfangen und nicht selbst versenden können.<br />

easily connected to an <strong>in</strong>terrupt controller, i.e. when asserted an <strong>in</strong>terrupt may be generated.<br />

Die Ports für den FSL s<strong>in</strong>d <strong>in</strong> dem Modul fsl.vhd wie folgt deklariert:<br />

FSL_V20 Bus Operation<br />

entity fsl is<br />

Port(<br />

-- Bus protocol ports , do not add or delete.<br />

FSL_Clk : <strong>in</strong> std_logic;<br />

X-Ref Target - Figure 2<br />

FSL_Rst : <strong>in</strong> std_logic;<br />

FSL_S_Read : out std_logic;<br />

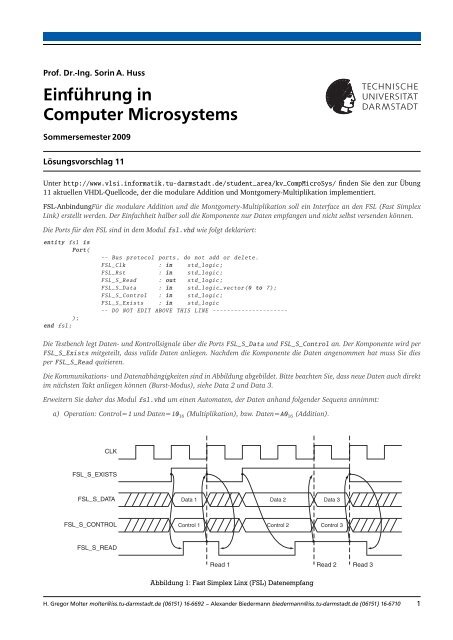

CLK<br />

FSL_S_Data : <strong>in</strong> std_logic_vector(0 to 7);<br />

FSL_S_Control : <strong>in</strong> std_logic;<br />

FSL_M_FULL FSL_S_Exists : <strong>in</strong> std_logic<br />

-- DO NOT EDIT ABOVE THIS LINE ---------------------<br />

);<br />

end fsl;<br />

FSL_M_WRITE<br />

Die Testbench legt Daten- und Kontrollsignale über die Ports FSL_S_Data und FSL_S_Control an. Der Komponente wird per<br />

FSL_S_Exists FSL_M_DATA mitgeteilt, dass valide Data Daten 1 anliegen. Nachdem Data 2 dieData Komponente 3 die Daten angenommen Data hat 4 muss Sie dies<br />

per FSL_S_Read quitieren.<br />

Die Kommunikations- und Datenabhängigkeiten s<strong>in</strong>d <strong>in</strong> Abbildung abgebildet. Bitte beachten Sie, dass neue Daten auch direkt<br />

FSL_M_CONTROL Control 1 Control 2 Control 3 Control 4<br />

im nächsten Takt anliegen können (Burst-Modus), siehe Data und Data 3.<br />

Write 1 Write 2 Write 3 Write 4<br />

Erweitern Sie daher das Modul fsl.vhd um e<strong>in</strong>en Automaten, der Daten anhand folgender Sequenz annimmt:<br />

a) Operation: Control=1 Figure und Daten=10 2: Fast Simplex 16 (Multiplikation), L<strong>in</strong>k (FSL) bzw. (v2.10a) Daten=A0 Write 16 (Addition). Operation<br />

DS449_02_062507<br />

X-Ref Target - Figure 3<br />

CLK<br />

FSL_S_EXISTS<br />

FSL_S_DATA<br />

Data 1 Data 2 Data 3<br />

FSL_S_CONTROL<br />

Control 1 Control 2 Control 3<br />

FSL_S_READ<br />

Read 1<br />

Read 2<br />

Figure 3: Abbildung Fast Simplex 1: Fast Simplex L<strong>in</strong>k (FSL) L<strong>in</strong>x (v2.10a) (FSL) Datenempfang Read Operation<br />

Read 3<br />

DS449_03_062507<br />

FSL Bus Write Operation<br />

H. Gregor Molter molter@iss.tu-darmstadt.de (06151) 16-6692 – Alexander Biedermann biedermann@iss.tu-darmstadt.de (06151) 16-6710 1<br />

The write to the FSL bus is controlled by the FSL_M_Write signal. The follow<strong>in</strong>g sequence of operations<br />

<strong>in</strong>dicate a write operation on the FSL bus. When the data <strong>in</strong> FSL_M_Data and control bit <strong>in</strong>

) Operand 1: Control=0 und Daten=Adresse von Operand 1 im RAM.<br />

c) Operand 2: Control=0 und Daten=Adresse von Operand 2 im RAM.<br />

d) Ergebnis: Control=0 und Daten=Adresse im RAM an die das Ergebnis geschrieben werden soll.<br />

Die mitgelieferte Testbench enthält jeweils e<strong>in</strong>en Test für die Addition und für die Multiplikation. Nach der Addition sollte an<br />

ram(6) = 006911 16 stehen. Bei der Multiplikation entsprechend ram(6) = 010B81 16 .<br />

Der Automat für die Kommunikation für den FSL:<br />

library IEEE;<br />

use IEEE.STD_LOGIC_1164.ALL;<br />

use IEEE.STD_LOGIC_ARITH.ALL;<br />

use IEEE.STD_LOGIC_UNSIGNED.ALL;<br />

use work.datatypes.all;<br />

entity fsl is<br />

Port(<br />

-- Bus protocol ports , do not add or delete.<br />

FSL_Clk : <strong>in</strong> std_logic;<br />

FSL_Rst : <strong>in</strong> std_logic;<br />

FSL_S_Read : out std_logic;<br />

FSL_S_Data : <strong>in</strong> std_logic_vector(0 to 7);<br />

FSL_S_Control : <strong>in</strong> std_logic;<br />

FSL_S_Exists : <strong>in</strong> std_logic<br />

-- DO NOT EDIT ABOVE THIS LINE ---------------------<br />

);<br />

end fsl;<br />

architecture Behavioral of fsl is<br />

component fsm is<br />

Port ( clock : <strong>in</strong> STD_LOGIC;<br />

reset : <strong>in</strong> STD_LOGIC;<br />

op1_addr : <strong>in</strong> type_wd_addr;<br />

op2_addr : <strong>in</strong> type_wd_addr;<br />

result_addr : <strong>in</strong> type_wd_addr;<br />

operation : <strong>in</strong> operation_type;<br />

start : <strong>in</strong> STD_LOGIC;<br />

ready : out STD_LOGIC);<br />

end component fsm;<br />

for all: fsm use entity work.fsm(Behavioral);<br />

type fsl_state_type is (WAIT_READY , CMD , OP1 , OP2 , RES , WAIT_READY_ZERO);<br />

signal r_op1 : type_wd_addr;<br />

signal r_op2 : type_wd_addr;<br />

signal r_res : type_wd_addr;<br />

signal r_operation : operation_type;<br />

signal r_start : STD_LOGIC;<br />

signal r_ready : STD_LOGIC;<br />

signal r_read : STD_LOGIC;<br />

signal FSL_STATE : fsl_state_type;<br />

beg<strong>in</strong><br />

component_fsm : fsm port map(<br />

clock => FSL_Clk ,<br />

reset => FSL_Rst ,<br />

op1_addr => r_op1 ,<br />

op2_addr => r_op2 ,<br />

result_addr => r_res ,<br />

operation => r_operation ,<br />

start => r_start ,<br />

ready => r_ready<br />

);<br />

FSL_S_Read

_op2 ’0’);<br />

r_res ’0’);<br />

r_operation

Formel berechnenDas RAM ist mit folgenden Werten <strong>in</strong>itialisiert:<br />

ram(i) Wert Bedeutung<br />

0 011BC3 16 Modul m<br />

1 005923 16 a<br />

2 000FEE 16 b<br />

3 00AFFE 16 c<br />

4 0092D3 16 R 2<br />

5 000001 16 Konstante 1<br />

6 000000 16 Frei zur Verwendung (tmp)<br />

Berechnen Sie mit Hilfe der Additions- und Montgomery-Multiplikations-Komponente die Formel (a + b) 2 c = r.<br />

Überlegen Sie wie <strong>in</strong> welcher Reihenfolge Sie die Operationen ausführen und wann Sie wie die Operanden <strong>in</strong> den Montgomery-<br />

Raum überführen und wieder zurück transformieren. Ihre Lösung sollte so wenig Operationen wie möglich enthalten! Erweitern<br />

Sie die Testbench dementsprechend, um obige Formel zu berechnen.<br />

E<strong>in</strong>e effiziente Lösung ist:<br />

a) Addition: tmp = a + b<br />

b) Montgomery-Multiplikation: b = MM tmp, R 2 (Transformation von a + b <strong>in</strong> den Montgomery-Raum (a + b)R)<br />

c) Montgomery-Multiplikation: a = MM (b, b) ((a + b) 2 im Montgomery-Raum ((a + b) 2 )R)<br />

d) Montgomery-Multiplikation: tmp = MM (a, c) (Berechnung Endergebnis (a + b) 2 c <strong>in</strong>klusive Rücktransformation aus<br />

dem Montgomery-Raum)<br />

Das Endergebnis ist 00002A 16 = 42 10 . Dies lässt sich mit Hilfe von nur 1 Addition und 3 Montgomery-Multiplikationen<br />

berechnen:<br />

...<br />

burst(OP_ADD , a_addr , b_addr , tmp_addr);<br />

burst(OP_MULT , tmp_addr , r2_addr , b_addr);<br />

burst(OP_MULT , b_addr , b_addr , a_addr);<br />

burst(OP_MULT , a_addr , c_addr , tmp_addr);<br />

... oder auch mit ...<br />

nonburst(OP_ADD , a_addr , b_addr , tmp_addr);<br />

nonburst(OP_MULT , tmp_addr , r2_addr , b_addr);<br />

nonburst(OP_MULT , b_addr , b_addr , a_addr);<br />

nonburst(OP_MULT , a_addr , c_addr , tmp_addr);<br />

...<br />

H. Gregor Molter molter@iss.tu-darmstadt.de (06151) 16-6692 – Alexander Biedermann biedermann@iss.tu-darmstadt.de (06151) 16-6710 4