Technische Grundlagen der Informatik 3. Musterlösung â Timings ...

Technische Grundlagen der Informatik 3. Musterlösung â Timings ... Technische Grundlagen der Informatik 3. Musterlösung â Timings ...

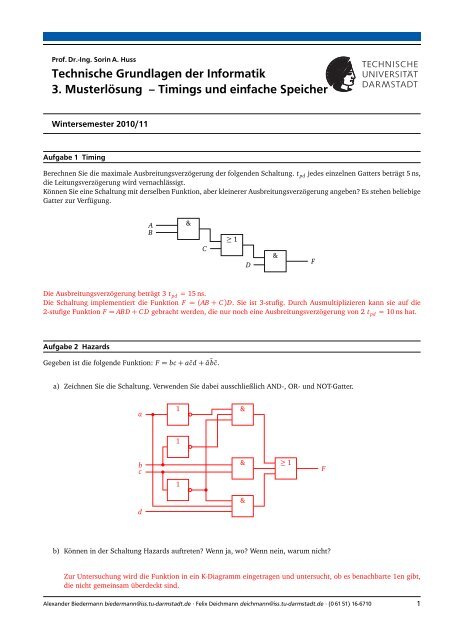

Prof. Dr.-Ing. Sorin A. Huss Technische Grundlagen der Informatik 3. Musterlösung – Timings und einfache Speicher Wintersemester 2010/11 Aufgabe 1 Timing Berechnen Sie die maximale Ausbreitungsverzögerung der folgenden Schaltung. t pd jedes einzelnen Gatters beträgt 5 ns, die Leitungsverzögerung wird vernachlässigt. Können Sie eine Schaltung mit derselben Funktion, aber kleinerer Ausbreitungsverzögerung angeben? Es stehen beliebige Gatter zur Verfügung. A B & C ≥ 1 D & F Die Ausbreitungsverzögerung beträgt 3 t pd = 15 ns. Die Schaltung implementiert die Funktion F = (AB + C)D. Sie ist 3-stufig. Durch Ausmultiplizieren kann sie auf die 2-stufige Funktion F = ABD + C D gebracht werden, die nur noch eine Ausbreitungsverzögerung von 2 t pd = 10 ns hat. Aufgabe 2 Hazards Gegeben ist die folgende Funktion: F = bc + a¯cd + ā¯b¯c. a) Zeichnen Sie die Schaltung. Verwenden Sie dabei ausschließlich AND-, OR- und NOT-Gatter. a 1 & 1 b c d & ≥ 1 F 1 & b) Können in der Schaltung Hazards auftreten? Wenn ja, wo? Wenn nein, warum nicht? Zur Untersuchung wird die Funktion in ein K-Diagramm eingetragen und untersucht, ob es benachbarte 1en gibt, die nicht gemeinsam überdeckt sind. Alexander Biedermann biedermann@iss.tu-darmstadt.de · Felix Deichmann deichmann@iss.tu-darmstadt.de · (0 61 51) 16-6710 1

- Seite 2 und 3: ab a cd 00 00 01 11 10 1 0 0 0 c 01

- Seite 4 und 5: T 1 & ≥ 1 D Q Q & C LK Q Q Aufgab

- Seite 6: 0 ns 5 ns 10 ns 15 ns 20 ns 25 ns 3

Prof. Dr.-Ing. Sorin A. Huss<br />

<strong>Technische</strong> <strong>Grundlagen</strong> <strong>der</strong> <strong>Informatik</strong><br />

<strong>3.</strong> Musterlösung – <strong>Timings</strong> und einfache Speicher<br />

Wintersemester 2010/11<br />

Aufgabe 1 Timing<br />

Berechnen Sie die maximale Ausbreitungsverzögerung <strong>der</strong> folgenden Schaltung. t pd jedes einzelnen Gatters beträgt 5 ns,<br />

die Leitungsverzögerung wird vernachlässigt.<br />

Können Sie eine Schaltung mit <strong>der</strong>selben Funktion, aber kleinerer Ausbreitungsverzögerung angeben? Es stehen beliebige<br />

Gatter zur Verfügung.<br />

A<br />

B<br />

&<br />

C<br />

≥ 1<br />

D<br />

&<br />

F<br />

Die Ausbreitungsverzögerung beträgt 3 t pd = 15 ns.<br />

Die Schaltung implementiert die Funktion F = (AB + C)D. Sie ist 3-stufig. Durch Ausmultiplizieren kann sie auf die<br />

2-stufige Funktion F = ABD + C D gebracht werden, die nur noch eine Ausbreitungsverzögerung von 2 t pd = 10 ns hat.<br />

Aufgabe 2 Hazards<br />

Gegeben ist die folgende Funktion: F = bc + a¯cd + ā¯b¯c.<br />

a) Zeichnen Sie die Schaltung. Verwenden Sie dabei ausschließlich AND-, OR- und NOT-Gatter.<br />

a<br />

1<br />

&<br />

1<br />

b<br />

c<br />

d<br />

&<br />

≥ 1<br />

F<br />

1<br />

&<br />

b) Können in <strong>der</strong> Schaltung Hazards auftreten? Wenn ja, wo? Wenn nein, warum nicht?<br />

Zur Untersuchung wird die Funktion in ein K-Diagramm eingetragen und untersucht, ob es benachbarte 1en gibt,<br />

die nicht gemeinsam überdeckt sind.<br />

Alexan<strong>der</strong> Bie<strong>der</strong>mann bie<strong>der</strong>mann@iss.tu-darmstadt.de · Felix Deichmann deichmann@iss.tu-darmstadt.de · (0 61 51) 16-6710 1

ab<br />

a<br />

cd<br />

00<br />

00 01 11 10<br />

1 0 0 0<br />

c<br />

01<br />

11<br />

10<br />

1 0 1 1<br />

0 1 1 0<br />

0 1 1 0<br />

d<br />

b<br />

An den blau markierten Stellen können potentiell Hazards auftreten.<br />

c) Simulieren Sie das Schaltnetz an den Übergängen<br />

• ab¯cd → abcd (1)<br />

• abcd → ab¯cd (2)<br />

• ā¯b¯cd → a¯b¯cd (3)<br />

• a¯b¯cd → ā¯b¯cd (4)<br />

Zeichnen Sie hierzu den Zeitverlauf <strong>der</strong> Ein- und Ausgangssignale auf. Gehen Sie davon aus, dass jedes Gatter eine<br />

Ausbreitungsverzögerung von 5 ns hat.<br />

0 ns 5 ns 10 ns 15 ns 20 ns 25 ns 30 ns<br />

a<br />

b<br />

c<br />

d<br />

a<br />

b<br />

c<br />

bc<br />

acd<br />

abc<br />

F<br />

0 ns 5 ns 10 ns 15 ns 20 ns 25 ns 30 ns<br />

a<br />

b<br />

c<br />

d<br />

a<br />

b<br />

c<br />

bc<br />

acd<br />

abc<br />

F<br />

Abbildung 1: abcd → abcd (1)<br />

Abbildung 2: abcd → abcd (2)<br />

2 Alexan<strong>der</strong> Bie<strong>der</strong>mann bie<strong>der</strong>mann@iss.tu-darmstadt.de · Felix Deichmann deichmann@iss.tu-darmstadt.de · (0 61 51) 16-6710

0 ns 5 ns 10 ns 15 ns 20 ns 25 ns 30 ns<br />

a<br />

b<br />

c<br />

d<br />

a<br />

b<br />

c<br />

bc<br />

acd<br />

abc<br />

F<br />

0 ns 5 ns 10 ns 15 ns 20 ns 25 ns 30 ns<br />

a<br />

b<br />

c<br />

d<br />

a<br />

b<br />

c<br />

bc<br />

acd<br />

abc<br />

F<br />

Abbildung 3: abcd → abcd (3)<br />

Abbildung 4: a¯b¯cd → ā¯b¯cd (4)<br />

d) Geben Sie eine Funktion an, die keine Hazards enthält.<br />

Bei <strong>der</strong> störimpulsfreien Funktion werden neue Terme an den kritischen Übergängen <strong>der</strong> Funktion hinzugefügt.<br />

Die komplette Funktion lautet: F(a, b, c, d) = bc + a¯cd + ā¯b¯c + abd + ¯b¯cd<br />

e) Erweitern Sie die ursprüngliche Schaltung mit den gewonnenen Erkenntnissen, damit diese störimpulsfrei wird.<br />

&<br />

a<br />

1<br />

&<br />

1<br />

&<br />

≥ 1<br />

F<br />

b<br />

c<br />

d<br />

1<br />

&<br />

&<br />

Aufgabe 3 Flip-Flops<br />

Entwerfen Sie ein T-Flip-Flop. Es wechselt den Zustand bei je<strong>der</strong> steigenden Taktflanke, wenn am Eingang T eine 1 anliegt,<br />

ansonsten behält es seinen Wert. Verwenden Sie zu Realisierung ein D-Flip-Flop und primitive Gatter.<br />

Die Übergangsgleichung eines T-Flip-Flops ist Q ′ = QT+QT. Somit muss diese Funktion vor den Eingang des verwendeten<br />

D-Flip-Flops geschaltet werden.<br />

Alexan<strong>der</strong> Bie<strong>der</strong>mann bie<strong>der</strong>mann@iss.tu-darmstadt.de · Felix Deichmann deichmann@iss.tu-darmstadt.de · (0 61 51) 16-6710 3

T<br />

1 &<br />

≥ 1<br />

D<br />

Q<br />

Q<br />

&<br />

C LK<br />

Q<br />

Q<br />

Aufgabe 4 Timing<br />

Berechnen Sie die Ausbreitungsverzögerung <strong>der</strong> folgenden Schaltung. t pd jedes einzelnen Gatters beträgt 4 ns. Geben Sie<br />

eine Schaltung an, die eine maximale Ausbreitungsverzögerung von 10 ns hat. Verwenden Sie dabei nur XOR-Gatter mit<br />

2 Eingängen.<br />

A<br />

B<br />

= 1<br />

C<br />

= 1<br />

D<br />

= 1<br />

F<br />

Die Ausbreitungsverzögerung beträgt 3 t pd = 12 ns.<br />

Eine Schaltung mit äquivalenter Funktion mit nur 8 ns Ausbreitungsverzögerung ist die folgende:<br />

A<br />

B<br />

= 1<br />

= 1<br />

F<br />

C<br />

D<br />

= 1<br />

Aufgabe 5 Register<br />

Es ist folgende Spezifikation eines Registers gegeben:<br />

• Als Speicherelement soll ein positiv flankengetriggertes D-Flip-Flop eingesetzt werden.<br />

• Außer dem Takt existieren zwei externe Steuereingänge, S 0 und S 1 , sowie drei externe Dateneingänge, SR, SL und<br />

DI.<br />

• Der aktuelle Inhalt D des Registers än<strong>der</strong>t sich gemäß folgenden Regeln:<br />

– S 0 = S 1 = 0 : ersetze D durch DI.<br />

– S 0 = 0, S 1 = 1: ersetze D durch SL<br />

– S 0 = 1, S 1 = 0: ersetze D durch SR<br />

– S 0 = S 1 = 1: aktuellen Wert halten.<br />

Zeichnen Sie ein Schaltbild für das Register.<br />

Vor den Eingang des Flip-Flops wird ein Multiplexer geschaltet, <strong>der</strong> in Abhängigkeit von den Steuereingängen den entsprechenden<br />

Wert an das Speicherelement weiterleitet.<br />

4 Alexan<strong>der</strong> Bie<strong>der</strong>mann bie<strong>der</strong>mann@iss.tu-darmstadt.de · Felix Deichmann deichmann@iss.tu-darmstadt.de · (0 61 51) 16-6710

DI<br />

0<br />

SR<br />

SL<br />

1<br />

4:1 MUX<br />

2<br />

3<br />

D<br />

Q<br />

D-Flip-Flop<br />

CLK<br />

C<br />

Q<br />

S 1<br />

S 0<br />

Aufgabe 6 Hazards<br />

Untersuchen Sie den folgenden Schaltplan auf Hazards. Gehen Sie von einer Ausbreitungsverzögerung von 5 ns je Gatter<br />

aus.<br />

B<br />

A<br />

1<br />

&<br />

C<br />

1<br />

&<br />

≥ 1<br />

F<br />

D<br />

1<br />

&<br />

Aus dem Schaltbild lässt sich die Funktion F = A¯C D + ĀB + ĀC ¯D ablesen. Diese wird zur Überprüfung in ein K-Diagramm<br />

eingetragen.<br />

AB<br />

C D<br />

00<br />

A<br />

00 01 11 10<br />

0 1 0 0<br />

C<br />

01<br />

11<br />

10<br />

0 1 1 1<br />

0 1 0 0<br />

1 1 0 0<br />

D<br />

B<br />

Im K-Diagramm erkennt man, dass ein kritischer Übergang zwischen ĀB ¯C D → AB ¯C D bzw. AB ¯C D → ĀB ¯C D liegt. Hier<br />

kann potentiell ein Störimpuls auftreten. Zur Überprüfung muss eine Simulation <strong>der</strong> fraglichen Stellen durchgeführt<br />

werden. Es müssen immer beide Richtungen betrachtet werden.<br />

Alexan<strong>der</strong> Bie<strong>der</strong>mann bie<strong>der</strong>mann@iss.tu-darmstadt.de · Felix Deichmann deichmann@iss.tu-darmstadt.de · (0 61 51) 16-6710 5

0 ns 5 ns 10 ns 15 ns 20 ns 25 ns 30 ns<br />

A<br />

A<br />

B<br />

C<br />

C<br />

D<br />

D<br />

AB<br />

AC D<br />

AC D<br />

F<br />

0 ns 5 ns 10 ns 15 ns 20 ns 25 ns 30 ns<br />

A<br />

A<br />

B<br />

C<br />

C<br />

D<br />

D<br />

AB<br />

AC D<br />

AC D<br />

F<br />

Abbildung 5: Simulation ĀB ¯C D → AB ¯C D<br />

Abbildung 6: Simulation AB ¯C D → ĀB ¯C D<br />

Durch die Simulation kann man erkennen, dass sich ein Störimpuls beim Übergang von AB ¯C D → ĀB ¯C D zeigt.<br />

6 Alexan<strong>der</strong> Bie<strong>der</strong>mann bie<strong>der</strong>mann@iss.tu-darmstadt.de · Felix Deichmann deichmann@iss.tu-darmstadt.de · (0 61 51) 16-6710