Parallelität und Pipelines

Parallelität und Pipelines Parallelität und Pipelines

2-Bit Sprungvorhersage • Falsche Vorhersage nur beim letzten Sprung aus Schleife heraus strongly taken taken predict taken weakly taken weakly not taken taken predict taken predict taken taken taken taken not taken taken predict not taken strongly not taken taken add $s1, $0, $0 # sum = 0 add $s0, $0, $0 # i = 0 addi $t0, $0, 10 # $t0 = 10 for: beq $s0, $t0, done # falls i == 10, springe add $s1, $s1, $s0 # sum = sum + i addi $s0, $s0, 1 # inkrementiere i j for done: WS 10/11 | Technische Grundlagen der Informatik - Repository - Prof. Sorin A. Huss | ‹Nr.›

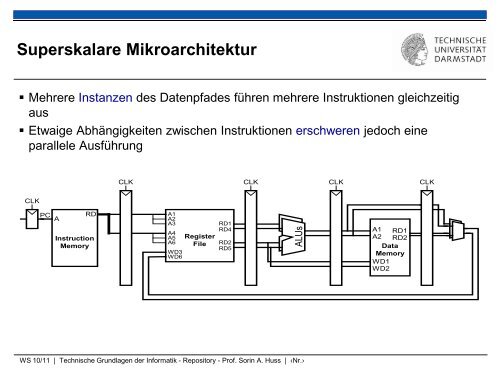

Superskalare Mikroarchitektur • Mehrere Instanzen des Datenpfades führen mehrere Instruktionen gleichzeitig aus • Etwaige Abhängigkeiten zwischen Instruktionen erschweren jedoch eine parallele Ausführung CLK CLK CLK CLK CLK PC A RD Instruction Memory A1 A2 A3 A4 A5 A6 WD3 WD6 Register File RD1 RD4 RD2 RD5 ALUs A1 RD1 A2 RD2 Data Memory WD1 WD2 WS 10/11 | Technische Grundlagen der Informatik - Repository - Prof. Sorin A. Huss | ‹Nr.›

- Seite 1 und 2: Technische Grundlagen der Informati

- Seite 3 und 4: Parallelität • Zwei Arten von Pa

- Seite 5 und 6: Beispiel: Plätzchen backen • Wei

- Seite 7 und 8: Beispiel: Plätzchen backen (parall

- Seite 9 und 10: Räumliche Parallelität Latenz: Ze

- Seite 11 und 12: Zeitliche Parallelität Latenz: Zei

- Seite 13 und 14: Schaltung ohne Pipelining • Kriti

- Seite 15 und 16: Schaltung mit dreistufiger Pipeline

- Seite 17 und 18: Mikroarchitektur: Fortgeschrittene

- Seite 19 und 20: Sprungvorhersage • Idealer Pipeli

- Seite 21: 1-Bit Sprungvorhersage • Speicher

- Seite 25 und 26: Beispiel: Superskalare Ausführung

- Seite 27 und 28: Out-of-Order Mikroarchitektur • P

- Seite 29 und 30: Umbenennen von Registern lw $t0, 40

- Seite 31 und 32: Weitere Mikroarchitekturtechniken

- Seite 33 und 34: Multithreading auf Mikroarchitektur

- Seite 35: Weiterführende Literatur • Patte

Superskalare Mikroarchitektur<br />

• Mehrere Instanzen des Datenpfades führen mehrere Instruktionen gleichzeitig<br />

aus<br />

• Etwaige Abhängigkeiten zwischen Instruktionen erschweren jedoch eine<br />

parallele Ausführung<br />

CLK CLK CLK CLK<br />

CLK<br />

PC<br />

A<br />

RD<br />

Instruction<br />

Memory<br />

A1<br />

A2<br />

A3<br />

A4<br />

A5<br />

A6<br />

WD3<br />

WD6<br />

Register<br />

File<br />

RD1<br />

RD4<br />

RD2<br />

RD5<br />

ALUs<br />

A1 RD1<br />

A2 RD2<br />

Data<br />

Memory<br />

WD1<br />

WD2<br />

WS 10/11 | Technische Gr<strong>und</strong>lagen der Informatik - Repository - Prof. Sorin A. Huss | ‹Nr.›