Parallelität und Pipelines

Parallelität und Pipelines Parallelität und Pipelines

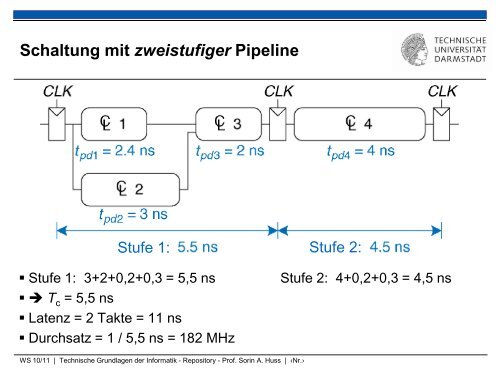

Schaltung mit zweistufiger Pipeline Stufe 1: Stufe 2: • Stufe 1: 3+2+0,2+0,3 = 5,5 ns • T c = 5,5 ns • Latenz = 2 Takte = 11 ns • Durchsatz = 1 / 5,5 ns = 182 MHz Stufe 2: 4+0,2+0,3 = 4,5 ns WS 10/11 | Technische Grundlagen der Informatik - Repository - Prof. Sorin A. Huss | ‹Nr.›

Schaltung mit dreistufiger Pipeline Stufe 1: Stufe 2: Stufe 3: • T c = 4,5ns • Latenz = 3 Takte = 13,5 ns • Durchsatz = 1 / 4,5 ns = 222 MHz WS 10/11 | Technische Grundlagen der Informatik - Repository - Prof. Sorin A. Huss | ‹Nr.›

- Seite 1 und 2: Technische Grundlagen der Informati

- Seite 3 und 4: Parallelität • Zwei Arten von Pa

- Seite 5 und 6: Beispiel: Plätzchen backen • Wei

- Seite 7 und 8: Beispiel: Plätzchen backen (parall

- Seite 9 und 10: Räumliche Parallelität Latenz: Ze

- Seite 11 und 12: Zeitliche Parallelität Latenz: Zei

- Seite 13: Schaltung ohne Pipelining • Kriti

- Seite 17 und 18: Mikroarchitektur: Fortgeschrittene

- Seite 19 und 20: Sprungvorhersage • Idealer Pipeli

- Seite 21 und 22: 1-Bit Sprungvorhersage • Speicher

- Seite 23 und 24: Superskalare Mikroarchitektur • M

- Seite 25 und 26: Beispiel: Superskalare Ausführung

- Seite 27 und 28: Out-of-Order Mikroarchitektur • P

- Seite 29 und 30: Umbenennen von Registern lw $t0, 40

- Seite 31 und 32: Weitere Mikroarchitekturtechniken

- Seite 33 und 34: Multithreading auf Mikroarchitektur

- Seite 35: Weiterführende Literatur • Patte

Schaltung mit zweistufiger Pipeline<br />

Stufe 1: Stufe 2:<br />

• Stufe 1: 3+2+0,2+0,3 = 5,5 ns<br />

• T c = 5,5 ns<br />

• Latenz = 2 Takte = 11 ns<br />

• Durchsatz = 1 / 5,5 ns = 182 MHz<br />

Stufe 2: 4+0,2+0,3 = 4,5 ns<br />

WS 10/11 | Technische Gr<strong>und</strong>lagen der Informatik - Repository - Prof. Sorin A. Huss | ‹Nr.›