Vorlesung Rechnerarchitektur - Fachbereich Informatik

Vorlesung Rechnerarchitektur - Fachbereich Informatik Vorlesung Rechnerarchitektur - Fachbereich Informatik

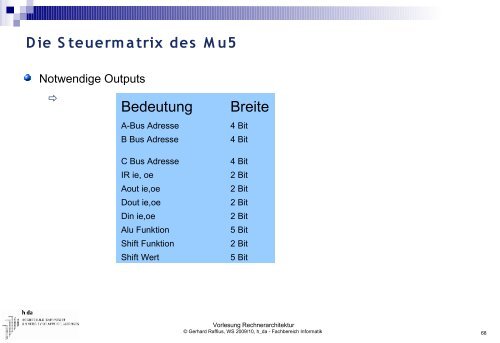

D ie S teuerm a trix des M u5 Notwendige Outputs Bedeutung A-Bus Adresse B Bus Adresse C Bus Adresse IR ie, oe Aout ie,oe Dout ie,oe Din ie,oe Alu Funktion Shift Funktion Shift Wert Breite 4 Bit 4 Bit 4 Bit 2 Bit 2 Bit 2 Bit 2 Bit 5 Bit 2 Bit 5 Bit Vorlesung Rechnerarchitektur © Gerhard Raffius, WS 2009/10, h_da - Fachbereich Informatik 68

V erbes s erte A dres s berec hnung Mu6 Datenpfad Adress Data In Aout PC ADD BB AA LR CC DD +2/4 IR Din SP ALU AAA R0-Rn A Shifter Dout Timing/Control Data Out Vorlesung Rechnerarchitektur © Gerhard Raffius, WS 2009/10, h_da - Fachbereich Informatik 69

- Seite 17 und 18: E in M U 0 P rog ra m m Loop LDA To

- Seite 19 und 20: D ie G rundfunktionen der A LU AB i

- Seite 21 und 22: D er M u1 D a tenpfa d Mu1 Datenpfa

- Seite 23 und 24: D er R es et Jeder Prozessor hat ei

- Seite 25 und 26: D er M ic roprog ra m C ounter S te

- Seite 27 und 28: D er Fetc h Z yklus im M u1 MU1 Dat

- Seite 29 und 30: D er S ta c k A push Speicher Der S

- Seite 31 und 32: U nterprog ra m m e Hauptprogramm U

- Seite 33 und 34: Indirekte A dres s ierung A STR Spe

- Seite 35 und 36: B es c hreibung des M ic roc odes d

- Seite 37 und 38: B es c hreibung des M ic roc odes d

- Seite 39 und 40: Z us ta nds bes c hreibung des La d

- Seite 41 und 42: D ie O pera tion P us h, der A kkum

- Seite 43 und 44: eding te S prüng e jge ACC15 = 1 1

- Seite 45 und 46: der S top B efehl stop 1 Der Stop B

- Seite 47 und 48: P roblem e des M u1 D es ig ns Der

- Seite 49 und 50: P roblem e des M U 0 D es ig ns Der

- Seite 51 und 52: K om plexe A dres s berec hnung en

- Seite 53 und 54: ela tive S prüng e .L1: .L2: movs

- Seite 55 und 56: K om plexe A dres s berec hnung : B

- Seite 57 und 58: R eg is tera rc hitektur Die Ergebn

- Seite 59 und 60: K ons equenzen a us der R eg is ter

- Seite 61 und 62: E ine V erbes s erte A LU Einsatz v

- Seite 63 und 64: V erbes s erung des internen B us s

- Seite 65 und 66: Fetc h Z yklus im M u5 In Aout steh

- Seite 67: D a tentra ns fer Adress Data In Ad

- Seite 71 und 72: B eis piel: s pekula tive B efehls

- Seite 73 und 74: P ipeline Die Pipeline erlaubt es d

- Seite 75 und 76: D ie H a rva rd A rc hitektur Durch

- Seite 77 und 78: 32 B it Ins truktionen 15 14 13 12

- Seite 79 und 80: A rithm etis c he und log is c he B

- Seite 81 und 82: D er A dditions befehl 15 9 8 7 6 5

- Seite 83 und 84: S ta c k-A rc hitektur Stacks werde

- Seite 85 und 86: R eg is ter-R eg is ter-A rc hitekt

D ie S teuerm a trix des M u5<br />

Notwendige Outputs<br />

<br />

Bedeutung<br />

A-Bus Adresse<br />

B Bus Adresse<br />

C Bus Adresse<br />

IR ie, oe<br />

Aout ie,oe<br />

Dout ie,oe<br />

Din ie,oe<br />

Alu Funktion<br />

Shift Funktion<br />

Shift Wert<br />

Breite<br />

4 Bit<br />

4 Bit<br />

4 Bit<br />

2 Bit<br />

2 Bit<br />

2 Bit<br />

2 Bit<br />

5 Bit<br />

2 Bit<br />

5 Bit<br />

<strong>Vorlesung</strong> <strong>Rechnerarchitektur</strong><br />

© Gerhard Raffius, WS 2009/10, h_da - <strong>Fachbereich</strong> <strong>Informatik</strong><br />

68