5. Teil MIPS - Ra.informatik.tu-darmstadt.de - Technische Universität ...

5. Teil MIPS - Ra.informatik.tu-darmstadt.de - Technische Universität ...

5. Teil MIPS - Ra.informatik.tu-darmstadt.de - Technische Universität ...

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Kapitel 10 (<strong>5.</strong> <strong>Teil</strong> <strong>MIPS</strong>):<br />

Pipeline-Implementierung<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2<br />

SS 2009<br />

R. Hoffmann<br />

FG Rechnerarchitek<strong>tu</strong>r<br />

<strong>Technische</strong> Universität Darmstadt<br />

In Anlehnung an das Patterson/Hennessy: Computer Organization & Design, 2 nd Edition, Chapter 6<br />

Es sind auch die Folien von Dr. M. G. Wahl (Univ. Siegen, Inst. Mikrosystemtechnik) und ähnliche<br />

aus <strong>de</strong>n Grundzügen <strong>de</strong>r Informatik II, SS03, von Prof. Dr. Oskar von Stryk verwen<strong>de</strong>t wor<strong>de</strong>n.

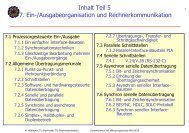

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Inhalt, Thema: Pipelining<br />

10–2<br />

<strong>Teil</strong> 1<br />

<strong>Teil</strong> 2<br />

• Prinzip<br />

• Bearbei<strong>tu</strong>ngszeit<br />

• Anwendungen<br />

• Arithmetisches Pipelining<br />

• Prozessor-Pipelining<br />

• Befehlspipelining<br />

• Befehlspipelining bei <strong>MIPS</strong><br />

• Pipeline-Entwurf<br />

• vom Eintakt-Rechenwerk zum<br />

Pipelining<br />

• Einfügen von Pipeline-<br />

Registern<br />

• Pipeline-Steuerung<br />

• Pipeline-Probleme<br />

• Allgemein<br />

• <strong>MIPS</strong><br />

1. Ressourcen-Konflikt<br />

2. Datenkonflikt<br />

3. Steuerflusskonflikt<br />

• Datenabhängigkeit<br />

• Datenhür<strong>de</strong><br />

• Software-Lösung<br />

• Forwarding<br />

• Stall<br />

• Steuerflusskonflikt<br />

• Weitere Leis<strong>tu</strong>ngssteigerung

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Grundlegen<strong>de</strong> Überlegungen<br />

10–3<br />

Bisher erreicht:<br />

• Mehrtakt-Implementierung<br />

für eine <strong>Teil</strong>menge <strong>de</strong>r <strong>MIPS</strong>-<br />

Befehle,<br />

• dadurch zwar mehrere<br />

Taktzyklen zur Abarbei<strong>tu</strong>ng eines<br />

Befehls, aber insgesamt<br />

schneller als bei Eintakt-<br />

Implementierung.<br />

• Auslas<strong>tu</strong>ng <strong>de</strong>r Hardware:<br />

Mehrtakt-Implementierung<br />

benutzt die Hardware-<br />

Einheiten (Ressourcen) nur<br />

in bestimmten<br />

Steuerzustän<strong>de</strong>n.<br />

Ziel:<br />

• Effizienzsteigerung durch<br />

Nutzung möglichst vieler<br />

Ressourcen zu je<strong>de</strong>m Zeitpunkt<br />

• Lösungsansatz: Parallele<br />

Bearbei<strong>tu</strong>ng mehrerer Befehle in<br />

Form einer<br />

Fließbandverarbei<strong>tu</strong>ng<br />

(Pipelining)

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Pipelining Prinzip (1)<br />

10–4<br />

• Ziel<br />

• Es ist eine Menge von<br />

ähnlichen<br />

Objekten/Ergebnissen in<br />

möglichst kurzer Zeit zu<br />

produzieren. (Maximierung<br />

<strong>de</strong>s Durchsatzes)<br />

• Voraussetzungen<br />

• Die Produktion kann in<br />

aufeinan<strong>de</strong>rfolgen<strong>de</strong>n<br />

<strong>Teil</strong>schritten erfolgen, die in<br />

etwa gleich lange dauern.<br />

• Es gibt ausreichend viele<br />

Ressourcen.<br />

Frauen am Fließband<br />

in <strong>de</strong>r<br />

Anzugschnei<strong>de</strong>rei <strong>de</strong>r<br />

Firma Bierbaum und<br />

Proenen in Köln<br />

Bierbaum und Proenen<br />

Köln, 1950-1960<br />

Photographie<br />

Bun<strong>de</strong>sbildstelle, Bonn<br />

• Lösung<br />

• Für je<strong>de</strong>n Bearbei<strong>tu</strong>ngsschritt<br />

wird eine Pipelines<strong>tu</strong>fe<br />

vorgesehen.<br />

• Alle Pipelines<strong>tu</strong>fen arbeiten<br />

parallel und liefern ihre<br />

<strong>Teil</strong>ergebnisse synchronisiert<br />

durch einen Takt an die<br />

nächste S<strong>tu</strong>fe weiter.

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Pipelining Prinzip (2)<br />

10–5<br />

Eingabeobjekte (Daten, Befehle, ...), Input-Stream: D1 .. Dm<br />

Darstellung: Füllung <strong>de</strong>r S<strong>tu</strong>fen über <strong>de</strong>r Zeit<br />

Takt: 1 2 3 4 5 6 7 8<br />

S<strong>tu</strong>fe1: D1 D2 D3 D4 D5<br />

S<strong>tu</strong>fe2: D1 D2 D3 D4 D5<br />

S<strong>tu</strong>fe3: D1 D2 D3 D4 D5<br />

S<strong>tu</strong>fe4: D1 D2 D3 D4 D5<br />

Füllen<br />

Ausgabeobjekte (Daten, Befehle, ...),<br />

Output-Stream<br />

Pipeline-<br />

Modus<br />

(Betriebsphase)<br />

Leeren

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Pipelining Prinzip (3)<br />

"multiple-clock-cycle pipeline diagram"<br />

Mehrzyklen-Pipelinediagramm<br />

10–6<br />

Aus dieser Darstellung kann man gut erkennen, zu welchem Zeitpunkt ein Da<strong>tu</strong>m<br />

welche S<strong>tu</strong>fe benutzt.<br />

Diese Darstellung eignet sich auch gut zur Ermittlung <strong>de</strong>r Datenabhängigkeiten<br />

zwischen <strong>de</strong>n Daten=Befehlen, s. z.B. 10-45<br />

Takt 1. 2. 3. 4. <strong>5.</strong> 6. 7. 8.<br />

Da<strong>tu</strong>m1 S<strong>tu</strong>fe1 S<strong>tu</strong>fe2 S<strong>tu</strong>fe3 S<strong>tu</strong>fe4<br />

Da<strong>tu</strong>m2 S<strong>tu</strong>fe1 S<strong>tu</strong>fe2 S<strong>tu</strong>fe3 S<strong>tu</strong>fe4<br />

Da<strong>tu</strong>m3 S<strong>tu</strong>fe1 S<strong>tu</strong>fe2 S<strong>tu</strong>fe3 S<strong>tu</strong>fe4<br />

Da<strong>tu</strong>m4 S<strong>tu</strong>fe1 S<strong>tu</strong>fe2 S<strong>tu</strong>fe3 S<strong>tu</strong>fe4<br />

Da<strong>tu</strong>m5 S<strong>tu</strong>fe1 S<strong>tu</strong>fe2 S<strong>tu</strong>fe3 S<strong>tu</strong>fe4<br />

Füllen<br />

Pipeline-<br />

Modus<br />

(Betriebsphase)<br />

Leeren<br />

Je<strong>de</strong>s Da<strong>tu</strong>m durchläuft sequentiell die n S<strong>tu</strong>fen.<br />

In <strong>de</strong>r Betriebsphase bearbeiten n S<strong>tu</strong>fen parallel n Daten.

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Bearbei<strong>tu</strong>ngszeit (1): ohne Pipelining<br />

10–7<br />

n=4<br />

m=5<br />

m<br />

n<br />

n = Anzahl <strong>de</strong>r S<strong>tu</strong>fen<br />

m = Anzahl <strong>de</strong>r zu bearbeiten<strong>de</strong>n Objekte<br />

T one = Gesamtbearbei<strong>tu</strong>ngszeit in einem Schritt<br />

Fall ohne Pipelining (n=1)<br />

• für m=1 Objekt: t ges (m=1,n=1) = T one<br />

Beispiel: n=1, m=1: T one =7<br />

n=1, m=10: T one = 70

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Bearbei<strong>tu</strong>ngszeit (2): nur ein Objekt<br />

10–8<br />

Fall mit n Pipelines<strong>tu</strong>fen (n>1)<br />

t1 t2 t3 t4<br />

• nur m=1 Objekt wird bearbeitet, die Verweildauer (Durchlaufzeit)<br />

beträgt dann<br />

• bei asynchroner Weitergabe: t ges (1,n) = Summe(t i ) = T asyn<br />

1<br />

• bei synchroner Weitergabe: t ges (1,n) = n t max = T syn<br />

mit t max = max (t i ) = Taktzeit<br />

1 wie bei einem mehrs<strong>tu</strong>figen<br />

Schaltnetz<br />

Beispiel: n=4, m=1, t1=1, t2=2, t3=1, t4=3<br />

T asyn = 1+2+1+3=7<br />

T syn = n t max = 4 * 3 = 12

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Bearbei<strong>tu</strong>ngszeit (3): m Objekte<br />

10–9<br />

Fall mit n Pipelines<strong>tu</strong>fen (n>1)<br />

• m Objekte wer<strong>de</strong>n bearbeitet, bei synchroner Weitergabe<br />

t ges (m,n) = n t max + (m-1) t max<br />

(für das erste Ergebnis, Latenzzeit) + (für die weiteren Ergebnisse)<br />

= (n-1) t max + m t max<br />

(Füllen Start-Up) + (für m Ergebnisse)<br />

t1 t2 t3 t4<br />

t ges (m,n) = T syn + (m-1) T syn /n<br />

Beispiel: n=4, m=10, t1=1, t2=2, t3=1, t4=3<br />

T syn = n * t max = 4 * 3 = 12<br />

t ges (10, 4) = 12 + (9) * 12/4 = 39 < 70 !!<br />

Vergleich: ohne Pipeline: mT one = 10*7=70

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Formel (Wdh.)<br />

10–10<br />

t ges (m,n) = T syn + (m-1) T syn /n = (n-1)*T syn /n + m*T syn /n<br />

• t ges Zeit zur Bearbei<strong>tu</strong>ng von m Objekten<br />

• n Anzahl <strong>de</strong>r S<strong>tu</strong>fen<br />

• m Anzahl <strong>de</strong>r Objekte<br />

• T syn Verweildauer, Durchlaufzeit<br />

• t max =T syn /n Taktzeit<br />

• (n-1)*T syn /n Start-Up-Time, Zeit um die Pipeline zu<br />

füllen<br />

• (n)*T syn /n Latenzzeit, Zeit bis zum ersten Ergebnis

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Speed-Up<br />

10–11<br />

• Speed-Up Z = Beschleunigungsfaktor =<br />

= Zeit bei sequentieller Verarbei<strong>tu</strong>ng<br />

Zeit bei Pipeline-Verarbei<strong>tu</strong>ng<br />

• für sehr große m: Start-Up-Time ist<br />

vernachlässigbar<br />

• t ges m t max , d. h. pro Takt ein neues Ergebnis<br />

• Z mT asyn / (mT syn /n) = n T asyn /T syn<br />

kleiner als 1 !<br />

Merke: Der Speed-Up zur Bearbei<strong>tu</strong>ng eines langen<br />

Datenstroms ist kleiner als n (Anzahl <strong>de</strong>r S<strong>tu</strong>fen).

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Pipelining: Eigenschaften<br />

10–12<br />

• Die Durchlaufzeit für eine<br />

einzelne Aufgabe ist beim<br />

Pipelining höher im Vergleich zur<br />

asynchronen Verarbei<strong>tu</strong>ng ohne<br />

Pipelining.<br />

• Die Pipelinegeschwindigkeit wird<br />

durch die langsamste S<strong>tu</strong>fe<br />

bestimmt.<br />

• Durchsatz/<br />

Übertragungsrate:<br />

• Anzahl <strong>de</strong>r übertragbaren<br />

Bytes/s, meist in MB/s<br />

• o<strong>de</strong>r auch Mbps (Megabit/s)<br />

bei serieller Übertragung<br />

• Beispiel: Warmwasserlei<strong>tu</strong>ng ....<br />

• Durchsatz steigt mit <strong>de</strong>r Anzahl<br />

n <strong>de</strong>r Pipelines<strong>tu</strong>fen, wenn<br />

• die Pipeline immer weiter in<br />

etwa gleich lange S<strong>tu</strong>fen geteilt<br />

wer<strong>de</strong>n kann.<br />

• die Zeit zum Zwischenspeichern<br />

<strong>de</strong>r <strong>Teil</strong>ergebnisse<br />

"vernachlässigt" wer<strong>de</strong>n kann<br />

(Pufferregister verursachen<br />

Zeitverzögerung).<br />

• Durchsatz wird reduziert durch<br />

• Registerübernahmezeiten<br />

• ungleiche Länge <strong>de</strong>r S<strong>tu</strong>fen<br />

• Zeit zum Füllen (am Anfang)<br />

und Leeren <strong>de</strong>r Pipeline (am<br />

En<strong>de</strong>)<br />

• Even<strong>tu</strong>elle Abhängigkeiten<br />

zwischen <strong>de</strong>n S<strong>tu</strong>fen

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Verschie<strong>de</strong>ne Anwendungen <strong>de</strong>s Pipelining<br />

10–13<br />

• Allgemein: Bearbei<strong>tu</strong>ng von<br />

Datenströmen<br />

• z.B. digitale<br />

Signalverabei<strong>tu</strong>ng, Vi<strong>de</strong>ound<br />

Audiostreams<br />

• Bearbei<strong>tu</strong>ng von Vektoren<br />

(in Vektorrechnern)<br />

• Arithmetisches Pipelining:<br />

Arithmetische Operationen<br />

wer<strong>de</strong>n in <strong>Teil</strong>schritten<br />

ausgeführt (z. B.<br />

Gleitkommaoperationen)<br />

• Prozessor-Pipelining: in<br />

je<strong>de</strong>r Bearbei<strong>tu</strong>ngss<strong>tu</strong>fe<br />

sitzt ein Prozessor.<br />

• Befehlspipelining, im<br />

folgen<strong>de</strong>n beim <strong>MIPS</strong><br />

• Befehl holen, <strong>de</strong>codieren und<br />

ausführen wird ständig<br />

wie<strong>de</strong>rholt

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Befehlspipelining bei <strong>MIPS</strong><br />

10–14<br />

• Die Ausführung eines<br />

komplexen Programms<br />

be<strong>de</strong>utet in <strong>de</strong>r Regel das<br />

Ausführen von Milliar<strong>de</strong>n<br />

von Mikrooperationen.<br />

Durchsatzmaximierung ist<br />

eines <strong>de</strong>r wesentlichen<br />

Entwurfsprobleme.<br />

• Was erleichtert die<br />

Implementierung (z. B. beim<br />

<strong>MIPS</strong>)?<br />

• Alle Befehle sollten in etwa<br />

gleich lang sein.<br />

• Registernummern sollten in<br />

allen Befehle an <strong>de</strong>rselben<br />

Stelle platziert sein.<br />

• Speicherzugriffe sollten nur in<br />

La<strong>de</strong>- und Speicherbefehlen<br />

vorkommen.<br />

• Je Befehl wird höchstens ein<br />

Rechenergebnis erzeugt, das in<br />

ein Register geschrieben wird.

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Befehlspipelining<br />

10–15<br />

• die auszuführen<strong>de</strong>n Schritte bei RISC-Befehlen,<br />

beispielhaft<br />

• Register-Register-Befehl<br />

IF Holen<br />

ID Decodieren, Register-Lesen<br />

EX ALU-Operation<br />

WB Register-Schreiben.<br />

• Load-Befehl<br />

IF Holen<br />

ID Decodieren, Register-Lesen<br />

EX Adresse berechnen<br />

MEM aus <strong>de</strong>m Cache o<strong>de</strong>r Hauptspeicher lesen<br />

WB Register-Schreiben.<br />

• Sprungbefehl<br />

IF Holen<br />

ID Decodieren, (Register-Lesen)<br />

EX Sprungadresse berechnen<br />

Befehlszähler neu setzen und schon vorverarbeitete Nachfolge-<br />

Befehle been<strong>de</strong>n o<strong>de</strong>r ihre Wirkung verhin<strong>de</strong>rn.

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

<strong>MIPS</strong>-Befehlszyklen am Beispiel lw<br />

10–16<br />

Zyklus 1<br />

Zyklus 2 Zyklus 3 Zyklus 4 Zyklus 5<br />

IF ID EX MEM WB<br />

IF: Fetch Befehl aus <strong>de</strong>m Programmspeicher<br />

ID: Decodiere Befehl und Read Register<br />

EX: (Ececute) Berechne die effektive Speicheradresse<br />

MEM: Read Daten aus <strong>de</strong>m Datenspeicher<br />

WB: Write Back die Daten ins Zielregister<br />

Die Überlegungen in Kapitel 5 sind auf die acht <strong>MIPS</strong>-Befehle lw, sw, add,<br />

sub, and, or, slt, beq beschränkt, die jeweils in maximal 5 Taktzyklen<br />

ausgeführt wer<strong>de</strong>n. Die übrigen <strong>MIPS</strong>-Befehle wer<strong>de</strong>n hier nicht untersucht.

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Erhöhung <strong>de</strong>s Befehlsdurchsatzes<br />

10–17<br />

Program<br />

execution<br />

or<strong>de</strong>r<br />

Time<br />

(in instructions)<br />

lw $1, 100($0)<br />

Eintakt-<strong>MIPS</strong>-Rechenwerk<br />

Instruction<br />

fetch<br />

2 4 6 8 10 12 14 16 18<br />

Reg<br />

ALU<br />

Data<br />

access<br />

Reg<br />

lw $2, 200($0)<br />

8 ns<br />

Instruction<br />

fetch<br />

Reg<br />

ALU<br />

Data<br />

access<br />

Reg<br />

lw $3, 300($0)<br />

Program<br />

execution<br />

Time<br />

or<strong>de</strong>r<br />

(in instructions)<br />

lw $1, 100($0)<br />

lw $2, 200($0)<br />

Instruction<br />

fetch<br />

2 ns<br />

Instruction<br />

fetch<br />

8 ns<br />

T asyn<br />

...<br />

8 ns<br />

T syn<br />

mit Pipelining<br />

2 4 6 8 10 12 14<br />

Data<br />

Beschleunigungsfaktor<br />

im Beispiel:<br />

Reg ALU<br />

Reg<br />

access<br />

Instruction<br />

Data<br />

Z 5 * 8/10 = 4<br />

Reg ALU<br />

Reg<br />

fetch<br />

access<br />

siehe Folie 10-11:<br />

lw $3, 300($0)<br />

2 ns<br />

Instruction<br />

fetch<br />

Reg<br />

ALU<br />

Data<br />

access<br />

Reg<br />

Z n T asyn /T syn<br />

2 ns 2 ns 2 ns 2 ns 2 ns

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Pipeline-Entwurf<br />

10–18<br />

• Vorgehen allgemein<br />

• Erst wird angenommen, dass je<strong>de</strong>r Befehl ein eigenes<br />

spezielles Operationswerk zur Verfügung hätte.<br />

Je<strong>de</strong>s Operationswerk besteht aus einer Folge von<br />

Operationen.<br />

• Dann wird die zeitliche Abarbei<strong>tu</strong>ng aller einzelnen<br />

Operationswerke in Zusammenhang gesetzt und daraus<br />

durch Überlagerung ein gemeinsames Operationswerk<br />

entworfen.<br />

• Vorgehen hier<br />

• Ausgangspunkt: Eintakt-Implementierung<br />

• Einfügen von Pipelineregistern.

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Eintakt-Implementierung (Wdh.)<br />

10–19<br />

M ux<br />

0<br />

4<br />

Add<br />

Instruction [31 26]<br />

Control<br />

RegDst<br />

Branch<br />

MemRead<br />

MemtoReg<br />

ALUOp<br />

MemWrite<br />

ALUSrc<br />

RegWrite<br />

Shift<br />

left 2<br />

Add<br />

ALU<br />

result<br />

1<br />

PCSrc<br />

PC<br />

Read<br />

address<br />

Instruction<br />

memory<br />

Instruction<br />

[31– 0]<br />

Instruction [25 21]<br />

Instruction [20 16]<br />

Instruction [15 11]<br />

Instruction [15 0]<br />

0<br />

M ux<br />

1<br />

Read<br />

register 1<br />

Read<br />

Read<br />

data 1<br />

register 2<br />

Registers Read<br />

Write<br />

data 2<br />

register<br />

Write<br />

data<br />

16 32<br />

Sign<br />

extend<br />

0<br />

M<br />

ux<br />

1<br />

ALU<br />

control<br />

Zero<br />

ALU ALU<br />

result<br />

Address<br />

Write<br />

data<br />

Data<br />

memory<br />

Read<br />

data<br />

M ux<br />

1<br />

0<br />

Instruction [5 0]

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Eintakt-Befehlsteilschritte<br />

10–20<br />

IF: Instructionfetch<br />

M ux<br />

0<br />

ID: Instruction<strong>de</strong>co<strong>de</strong>/<br />

register fileread<br />

EX: Execute/<br />

address calculation<br />

MEM: Memory access<br />

WB: Writeback<br />

1<br />

PC<br />

clk<br />

4<br />

Address<br />

Add<br />

Instruction<br />

memory<br />

Instruction<br />

Instruction<br />

Memory IM<br />

Read<br />

register 1<br />

Read<br />

Read<br />

data1<br />

register 2<br />

Registers Read<br />

data2<br />

Write<br />

register<br />

Write<br />

data<br />

clk<br />

16<br />

Sign<br />

extend<br />

32<br />

Shift<br />

left 2<br />

0<br />

M ux<br />

1<br />

Add Add result<br />

ALU Zero<br />

ALU<br />

result<br />

Data<br />

Memory DM<br />

Address<br />

Data<br />

memory<br />

Write<br />

data<br />

Read<br />

data<br />

M ux<br />

1<br />

0<br />

clk<br />

• Je<strong>de</strong>r Schritt bei Ausführung eines <strong>MIPS</strong>-Befehls wird von links nach<br />

rechts fortgeführt.<br />

• Zwei Ausnahmen: WB-Schritt und Wahl <strong>de</strong>s nächsten PC

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

vom Eintakt-Rechenwerk zum Pipelining<br />

10–21<br />

Program<br />

execution<br />

or<strong>de</strong>r<br />

(in instructions)<br />

Time (in clock cycles)<br />

CC 1 CC 2 CC 3 CC 4 CC 5 CC 6 CC 7<br />

lw $1, 100($0) IM Reg ALU DM Reg<br />

lw $2, 200($0)<br />

IM Reg ALU DM Reg<br />

lw $3, 300($0)<br />

IM Reg ALU DM Reg<br />

Register lesen (in <strong>de</strong>r 2. Hälfte <strong>de</strong>s Taktzyklus)<br />

Register schreiben (in <strong>de</strong>r 1. Hälfte <strong>de</strong>s Taktzyklus)<br />

• Befehlsspeicher IM wird nur in jeweils einer <strong>de</strong>r 5 S<strong>tu</strong>fen eines Befehls<br />

verwen<strong>de</strong>t, d. h. kann während <strong>de</strong>r übrigen 4 S<strong>tu</strong>fen von an<strong>de</strong>ren<br />

Befehlen verwen<strong>de</strong>t wer<strong>de</strong>n.<br />

• Um <strong>de</strong>n Datenwert eines einzelnen Befehls für die übrigen 4 S<strong>tu</strong>fen zu<br />

erhalten, muss <strong>de</strong>r aus <strong>de</strong>m IM gelesen Wert in einem Register<br />

zwischengespeichert wer<strong>de</strong>n. Pipeline-Register zwischen S<strong>tu</strong>fen.

Instruction<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Einfügen von Pipeline-Registern<br />

M<br />

ux<br />

0<br />

4 Pipeline-Register<br />

puffern die noch benötigten Informationen und <strong>Teil</strong>ergebnisse<br />

10–22<br />

1<br />

IF/ID (64 Bit) ID/EX (128 Bit) EX/MEM (97 Bit) MEM/WB (64 Bit)<br />

Add<br />

PC<br />

posedge<br />

clk<br />

4<br />

Address<br />

Instruction<br />

memory<br />

write on<br />

negedge<br />

clk<br />

Read<br />

register 1<br />

Read<br />

Read<br />

data 1<br />

register 2<br />

Registers Read<br />

data 2<br />

Write<br />

register<br />

Write<br />

data<br />

16<br />

Sign<br />

extend<br />

32<br />

Shift<br />

left 2<br />

0<br />

M<br />

ux<br />

1<br />

Add<br />

result<br />

Add<br />

Zero<br />

ALU ALU<br />

result<br />

Write<br />

data<br />

posedge<br />

clk<br />

Address<br />

Data<br />

memory<br />

Read<br />

data<br />

M<br />

ux<br />

1<br />

0<br />

IF/ID: 64 Bit (32-Bit<br />

für Befehlswort und<br />

32-Bit für erhöhte PC-<br />

Adresse)<br />

Modifiziertes Operationswerk: Nummer <strong>de</strong>s Write-Registers und zu<br />

schreiben<strong>de</strong>r Datenwert kommen aus Pipeline-Register MEM/WB.

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Darstellung <strong>de</strong>r Aktivitäten<br />

• Darstellung <strong>de</strong>r benutzten physikalischen Ressourcen<br />

Program<br />

execution<br />

or<strong>de</strong>r<br />

(in instructions)<br />

lw $10, 20($1)<br />

Time (in clock cycles)<br />

CC 1 CC 2 CC 3 CC 4 CC 5 CC 6<br />

IM Reg ALU DM Reg<br />

10–23<br />

sub $11, $2, $3<br />

not<br />

used<br />

IM Reg ALU DM Reg<br />

Program<br />

execution<br />

or<strong>de</strong>r<br />

(in instructions)<br />

lw $10, $20($1)<br />

sub $11, $2, $3<br />

Time ( in clock cycles)<br />

CC 1 CC 2 CC 3 CC 4 CC 5 CC 6<br />

Instruction<br />

fetch<br />

In dieser Darstellung (multiple-clock-cycle pipeline<br />

diagram) ist <strong>de</strong>r ak<strong>tu</strong>ellste Befehlsschritt rechts unten.<br />

• konventionelle Darstellung mit Namen <strong>de</strong>r einzelnen Schritte:<br />

Instruction<br />

<strong>de</strong>co<strong>de</strong><br />

Instruction<br />

fetch<br />

Execution<br />

Instruction<br />

<strong>de</strong>co<strong>de</strong><br />

Data<br />

access<br />

Execution<br />

Write back<br />

Data<br />

access<br />

Write back

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Betrieb <strong>de</strong>r Pipeline<br />

10–24<br />

• Optimale Nutzung, wenn 5 Befehle gleichzeitig aktiv<br />

in <strong>de</strong>n 5 S<strong>tu</strong>fen<br />

• Anfangsphase: Füllen <strong>de</strong>r Pipeline<br />

• Betriebsphase: Gleichzeitige Bearbei<strong>tu</strong>ng in <strong>de</strong>r<br />

Pipeline (eingeschwungene Pipeline)<br />

• Endphase: Leeren <strong>de</strong>r Pipeline<br />

• Beispiel:<br />

• lw<br />

• sub

Instruction<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Beispiel zur Pipeline (1): lw; sub<br />

10–25<br />

lw$10, 20($1)<br />

Instruction fetch<br />

M<br />

ux<br />

0<br />

In dieser Darstellung (single-cycle pipeline diagram)<br />

ist <strong>de</strong>r ak<strong>tu</strong>ellste Befehlsschritt links.<br />

1<br />

IF/ID ID/EX<br />

EX/MEM MEM/WB<br />

Add<br />

4<br />

Shift<br />

left 2<br />

Add<br />

result<br />

Add<br />

PC<br />

Address<br />

Instruction<br />

memory<br />

Read<br />

register 1<br />

Read<br />

Read<br />

data 1<br />

register 2<br />

Registers Read<br />

data 2<br />

Write<br />

register<br />

Write<br />

data<br />

16<br />

Sign<br />

extend<br />

32<br />

0<br />

M<br />

ux<br />

1<br />

Zero<br />

ALU ALU<br />

result<br />

Address<br />

Write<br />

data<br />

Data<br />

memory<br />

Read<br />

data<br />

M<br />

ux<br />

1<br />

0<br />

clock Clock 11

Instruction<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Beispiel zur Pipeline (2)<br />

10–26<br />

sub $11, $2, $3<br />

Instruction fetch<br />

lw$10, 20($1)<br />

Instruction <strong>de</strong>co<strong>de</strong><br />

M<br />

ux<br />

0<br />

1<br />

IF/ID ID/EX<br />

EX/MEM MEM/WB<br />

Add<br />

4<br />

Shift<br />

left 2<br />

Add<br />

result<br />

Add<br />

PC<br />

Address<br />

Instruction<br />

memory<br />

Read<br />

register 1<br />

Read<br />

Read<br />

data 1<br />

register 2<br />

Registers Read<br />

data 2<br />

Write<br />

register<br />

Write<br />

data<br />

16<br />

Sign<br />

extend<br />

32<br />

0<br />

M<br />

ux<br />

1<br />

Zero<br />

ALU ALU<br />

result<br />

Address<br />

Write<br />

data<br />

Data<br />

memory<br />

Read<br />

data<br />

M<br />

ux<br />

1<br />

0<br />

clock Clock 22

Instruction<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Beispiel zur Pipeline (3)<br />

10–27<br />

sub $11, $2, $3<br />

Instruction <strong>de</strong>co<strong>de</strong><br />

lw$10, 20($1)<br />

Execution<br />

M<br />

ux<br />

0<br />

1<br />

IF/ID ID/EX<br />

EX/MEM MEM/WB<br />

Add<br />

4<br />

Shift<br />

left 2<br />

Add<br />

result<br />

Add<br />

PC<br />

Address<br />

Instruction<br />

memory<br />

Read<br />

register 1<br />

Read<br />

Read<br />

data1<br />

register 2<br />

Registers Read<br />

data2<br />

Write<br />

register<br />

Write<br />

data<br />

16<br />

Sign<br />

extend<br />

32<br />

0<br />

M<br />

ux<br />

1<br />

Zero<br />

ALU ALU<br />

result<br />

Address<br />

Write<br />

data<br />

Data<br />

memory<br />

Read<br />

data<br />

M<br />

ux<br />

1<br />

0<br />

Clock 3<br />

clock 3

Instruction<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Beispiel zur Pipeline (4)<br />

10–28<br />

M<br />

ux<br />

0<br />

1<br />

sub $11, $2, $3<br />

Execution<br />

lw$10, 20($1)<br />

Memory<br />

IF/ID ID/EX<br />

EX/MEM MEM/WB<br />

Add<br />

4<br />

Shift<br />

left 2<br />

Add<br />

result<br />

Add<br />

PC<br />

Address<br />

Instruction<br />

memory<br />

Read<br />

register 1<br />

Read<br />

Read<br />

data1<br />

register 2<br />

Registers Read<br />

data2<br />

Write<br />

register<br />

Write<br />

data<br />

16<br />

Sign<br />

extend<br />

32<br />

0<br />

M<br />

ux<br />

1<br />

Zero<br />

ALU ALU<br />

result<br />

Address<br />

Write<br />

data<br />

Data<br />

memory<br />

Read<br />

data<br />

M<br />

ux<br />

1<br />

0<br />

clock Clock 4

Instruction<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Beispiel zur Pipeline (5)<br />

10–29<br />

M ux<br />

0<br />

1<br />

sub$11, $2, $3<br />

Memory<br />

lw$10, 20($1)<br />

Write back<br />

IF/ID<br />

ID/EX<br />

EX/MEM<br />

MEM/WB<br />

Add<br />

4<br />

Shift<br />

left 2<br />

Add<br />

result<br />

Add<br />

PC<br />

Address<br />

Instruction<br />

memory<br />

Read<br />

register 1<br />

Read<br />

Read<br />

data1<br />

register 2<br />

Registers Read<br />

data2<br />

Write<br />

register<br />

Write<br />

data<br />

16<br />

Sign<br />

extend<br />

32<br />

0<br />

M ux<br />

1<br />

Zero<br />

ALU ALU<br />

result<br />

Address<br />

Write<br />

data<br />

Data<br />

memory<br />

Read<br />

data<br />

M<br />

ux<br />

1<br />

0<br />

clock Clock 55

Instruction<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Beispiel zur Pipeline (6)<br />

10–30<br />

M<br />

ux<br />

0<br />

1<br />

sub $11, $2, $3<br />

Write back<br />

IF/ID<br />

ID/EX<br />

EX/MEM<br />

MEM/WB<br />

Add<br />

4<br />

Shift<br />

left 2<br />

Add<br />

result<br />

Add<br />

PC<br />

Address<br />

Instruction<br />

memory<br />

Read<br />

register 1<br />

Read<br />

Read<br />

data1<br />

register 2<br />

Registers Read<br />

data2<br />

Write<br />

register<br />

Write<br />

data<br />

16<br />

Sign<br />

extend<br />

32<br />

0<br />

M<br />

ux<br />

1<br />

Zero<br />

ALU ALU<br />

result<br />

Address<br />

Write<br />

data<br />

Data<br />

memory<br />

Read<br />

data<br />

M<br />

ux<br />

1<br />

0<br />

clock Clock 66

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Entwicklung <strong>de</strong>r Pipeline-Steuerung<br />

10–31<br />

• Verfahren<br />

• Nicht nur <strong>de</strong>r Datenpfad <strong>de</strong>r Eintakt-Impl. wird in<br />

Pipelines<strong>tu</strong>fen zerlegt,<br />

• auch <strong>de</strong>r Kontrollpfad

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Eintakt-Implementierung + Pipelineregister<br />

10–32<br />

auch die Steuersignale müssen "gepipet" wer<strong>de</strong>n<br />

M ux<br />

0<br />

4<br />

Add<br />

Instruction [31 26]<br />

Control<br />

RegDst<br />

Branch<br />

MemRead<br />

MemtoReg<br />

ALUOp<br />

MemWrite<br />

ALUSrc<br />

RegWrite<br />

Shift<br />

left 2<br />

Add<br />

ALU<br />

result<br />

1<br />

PCSrc<br />

PC<br />

Read<br />

address<br />

Instruction<br />

memory<br />

Instruction<br />

[31– 0]<br />

Instruction [25 21]<br />

Instruction [20 16]<br />

Instruction [15 11]<br />

Instruction [15 0]<br />

0<br />

M ux<br />

1<br />

Read<br />

register 1<br />

Read<br />

Read<br />

data 1<br />

register 2<br />

Registers Read<br />

Write<br />

data 2<br />

register<br />

Write<br />

data<br />

16 32<br />

Sign<br />

extend<br />

0<br />

M<br />

ux<br />

1<br />

ALU<br />

control<br />

Zero<br />

ALU ALU<br />

result<br />

Address<br />

Write<br />

data<br />

Data<br />

memory<br />

Read<br />

data<br />

M ux<br />

1<br />

0<br />

Instruction [5 0]

Instruction<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Pipeline-Steuersignale<br />

10–33<br />

PCSrc<br />

0<br />

IF/ID ID/EX EX/MEM MEM/WB<br />

4<br />

RegWrite<br />

Shift<br />

left 2<br />

Add<br />

Add<br />

result<br />

Branch<br />

PC<br />

Address<br />

Instruction<br />

memory<br />

M<br />

ux<br />

0<br />

1<br />

Add<br />

Read<br />

register 1<br />

Read<br />

Read<br />

data 1<br />

register 2<br />

Registers Read<br />

Write data 2<br />

register<br />

Write<br />

data<br />

Instruction<br />

[15–0] 16 32<br />

Sign<br />

extend<br />

ALUSrc<br />

0<br />

M<br />

ux<br />

1<br />

6<br />

ALU<br />

control<br />

Zero<br />

ALU ALU<br />

result<br />

Address<br />

Write<br />

data<br />

MemWrite<br />

Data<br />

memory<br />

MemRead<br />

Read<br />

data<br />

MemtoReg<br />

1<br />

M<br />

ux<br />

0<br />

Instruction<br />

[20–16]<br />

Instruction<br />

[15–11]<br />

M<br />

ux<br />

1<br />

ALUOp<br />

RegDst

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Pipeline-Steuerung<br />

10–34<br />

• Gleiche Be<strong>de</strong>u<strong>tu</strong>ng <strong>de</strong>r Steuersignale wie beim<br />

Eintakt-Rechenwerk<br />

• Gruppierung <strong>de</strong>r Steuersignale nach <strong>de</strong>n 5 S<strong>tu</strong>fen.<br />

Was muss auf welcher S<strong>tu</strong>fe gesteuert wer<strong>de</strong>n?<br />

• IF:<br />

• ID:<br />

• EX:<br />

• MEM:<br />

• WB:<br />

Befehl la<strong>de</strong>n und PC erhöhen<br />

Decodiere Befehl / La<strong>de</strong> Register<br />

Ausführung<br />

Speicher read/write<br />

Zurückschreiben von Daten ins Zielregister<br />

• Durchreichen <strong>de</strong>r Steuersignale bzw. <strong>de</strong>s<br />

Opco<strong>de</strong>s

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Pipeline-Steuerung<br />

• Gruppierung <strong>de</strong>r Steuersignale nach <strong>de</strong>n letzten 3 Pipelines<strong>tu</strong>fen:<br />

• Durchreichen von Steuersignalen über erweiterte Pipeline-Register wie die Daten:<br />

Execution/Address Calculation<br />

stage control lines<br />

Memory access stage<br />

control lines<br />

Write-back<br />

stage control<br />

lines<br />

Instruction<br />

Reg<br />

Dst<br />

ALU<br />

Op1<br />

ALU<br />

Op0<br />

ALU<br />

Src Branch<br />

Mem<br />

Read<br />

Mem<br />

Write<br />

Reg<br />

write<br />

Mem to<br />

Reg<br />

R-format 1 1 0 0 0 0 0 1 0<br />

lw 0 0 0 1 0 1 0 1 1<br />

sw X 0 0 1 0 0 1 0 X<br />

beq X 0 1 0 1 0 0 0 X<br />

10–35<br />

EX M WB<br />

WB<br />

Instruction<br />

Control<br />

M<br />

WB<br />

EX<br />

M<br />

WB<br />

IF/ID ID/EX EX/MEM MEM/WB

RegWrite<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Pipeline mit Steuerwerk<br />

• Steuersignale für die<br />

letzten 3 Pipelines<strong>tu</strong>fen<br />

wer<strong>de</strong>n in ID-S<strong>tu</strong>fe erzeugt<br />

und dann durchgereicht.<br />

10–36<br />

PCSrc<br />

M ux<br />

0<br />

1<br />

Control<br />

ID/EX<br />

WB<br />

M<br />

EX/MEM<br />

WB<br />

MEM/WB<br />

IF/ID<br />

EX<br />

M<br />

WB<br />

Add<br />

PC<br />

4<br />

Address<br />

Instruction<br />

memory<br />

Ausführliche Beispiele<br />

für Pipelineabarbei<strong>tu</strong>ng<br />

samt<br />

Steuersignalen bei<br />

Patterson/Hennessy<br />

in Chapter 6.3, 6.4.<br />

Instruction<br />

Read<br />

register 1<br />

Read<br />

Read<br />

data 1<br />

register 2<br />

Registers Read<br />

Write data 2<br />

register<br />

Write<br />

data<br />

Instruction<br />

[15–0]<br />

Instruction<br />

[20–16]<br />

Instruction<br />

[15–11]<br />

16 32<br />

Sign<br />

extend<br />

Shift<br />

left 2<br />

M ux<br />

0<br />

0<br />

M ux<br />

1<br />

6<br />

1<br />

RegDst<br />

Add result<br />

Add<br />

ALU<br />

control<br />

ALUSrc<br />

Zero<br />

ALU ALU<br />

result<br />

ALUOp<br />

Branch<br />

Write<br />

data<br />

MemWrite<br />

Address<br />

Data<br />

memory<br />

Read<br />

data<br />

MemRead<br />

MemtoReg<br />

M<br />

ux<br />

1<br />

0

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Zusammenfassung <strong>Teil</strong> 1<br />

10–37<br />

• Pipeline-Prinzip<br />

• Höherer Durchsatz bei<br />

Datenströmen<br />

• aber: Latenzzeit<br />

• Grenzen:<br />

Registerübernahmezeiten,<br />

ungleiche Sufenlängen<br />

• Anwendungen<br />

• Datenströme<br />

• Arithmetisches Pipelining<br />

• Prozessor-Pipelining<br />

• Befehlspipelining<br />

• Befehlspipelining bei <strong>MIPS</strong><br />

• IF: Instruction Fetch<br />

• ID: Instruction Deco<strong>de</strong> (auch<br />

Register lesen)<br />

• EX:<br />

• Execute<br />

• Speicheradressberechnung<br />

• NextPC-Berechnung<br />

• MEM: Speicher<br />

lesen/schreiben<br />

• WB: Register schreiben<br />

• Pipeline-Steuerung<br />

• Durchreichen <strong>de</strong>s Opco<strong>de</strong>s<br />

und von bereits <strong>de</strong>codierten<br />

Steuersignalen

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

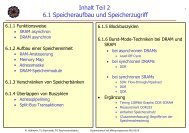

<strong>Teil</strong> 2<br />

10–38<br />

• Pipeline-Probleme<br />

• Allgemein<br />

1. Ressourcen-Konflikt<br />

2. Datenkonflikt<br />

3. Steuerflusskonflikt<br />

• <strong>MIPS</strong><br />

• Datenabhängigkeit<br />

• Datenhür<strong>de</strong><br />

• Software-Lösung<br />

• Forwarding<br />

• Stall<br />

• Steuerflusskonflikt<br />

• Weitere Leis<strong>tu</strong>ngssteigerung

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Pipeline-Probleme (1)<br />

10–39<br />

• In <strong>de</strong>r Pipeline befin<strong>de</strong>n<br />

sich immer bis zu n Befehle<br />

gleichzeitig in Bearbei<strong>tu</strong>ng.<br />

• Die Befehle konkurrieren<br />

um die Ressourcen<br />

• Zwischen <strong>de</strong>n Befehlen gibt<br />

es unterschiedliche<br />

Abhängigkeiten, die bei<br />

<strong>de</strong>r Pipelineverarbei<strong>tu</strong>ng zu<br />

Si<strong>tu</strong>ationen (Hazards,<br />

Hemmnisse, Hür<strong>de</strong>n,<br />

Konflikte) führen, die in <strong>de</strong>r<br />

Hardware o<strong>de</strong>r Software<br />

speziell behan<strong>de</strong>lt wer<strong>de</strong>n<br />

müssen.<br />

• Unterschiedliche<br />

Komplexität <strong>de</strong>r Befehle<br />

erschwert <strong>de</strong>n Pipeline-<br />

Entwurf<br />

• Anzahl <strong>de</strong>r nacheinan<strong>de</strong>r<br />

auszuführen<strong>de</strong>n<br />

Mikrooperationen ist nicht<br />

konstant (variiert je nach<br />

Befehl und kann von Daten<br />

in <strong>de</strong>r Ausführung abhängig<br />

sein)

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Probleme (2)<br />

10–40<br />

• Die Befehlspipelines<strong>tu</strong>fen können nicht immer<br />

genutzt wer<strong>de</strong>n, wegen <strong>de</strong>r möglichen Konflikte<br />

1. Ressourcen-Konflikt (Struk<strong>tu</strong>rkonflikt, struc<strong>tu</strong>ral<br />

Hazard) <br />

2. Datenkonflikt (Data Hazard, Datenhür<strong>de</strong>) <br />

3. Steuerflusskonflikt (Control Hazard,<br />

Sprungabhängigkeit, Procedural Depen<strong>de</strong>ncy)

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

1. Ressourcen-Konflikt<br />

10–41<br />

• entsteht durch die<br />

begrenzten Ressourcen<br />

• Die Anzahl, Art und<br />

Reihenfolge <strong>de</strong>r Zugriffe<br />

auf die Hardware-Einheiten<br />

(wie Speicher, Register,<br />

ALUs, Adressrechenwerk,<br />

MMU, Cache) variiert je<br />

nach Befehl.<br />

• Bei <strong>de</strong>r parallelen<br />

Ausführung in <strong>de</strong>r Pipeline<br />

kommt es zu<br />

Zugriffskonflikten, wenn<br />

nicht genügend viele<br />

Hardware-<br />

Ausführungseinheiten bzw.<br />

Zugriffsmöglichkeiten zur<br />

Verfügung stehen.<br />

• Auflösung: Wartezyklen<br />

(Bubbles)

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

2. Datenhür<strong>de</strong>, Datenkonflikt<br />

10–42<br />

• entsteht durch<br />

Datenabhängigkeiten<br />

• (echte Datenabhängigkeit)<br />

Der Befehl i+k, k>1 benötigt das<br />

Ergebnis <strong>de</strong>s Befehls i, <strong>de</strong>r sich<br />

noch in <strong>de</strong>r Berechnung befin<strong>de</strong>t<br />

(true data <strong>de</strong>pen<strong>de</strong>ncy)<br />

• Auflösung: Wartezyklen,<br />

Forwarding<br />

• (falsche Datenabhängigkeit,<br />

name <strong>de</strong>pen<strong>de</strong>ncy)<br />

• entsteht nur durch Umordnung<br />

<strong>de</strong>r Ausführungsreihenfolge<br />

(out-of-or<strong>de</strong>r execution) bei<br />

mo<strong>de</strong>rnen Prozessoren, dabei<br />

können sich Befehle überholen.<br />

Ist bei <strong>de</strong>m <strong>MIPS</strong> nicht<br />

möglich. Die Konflikte sind<br />

• Zielregisterkonflikt (zwei<br />

Befehle wollen gleichzeitig in ein<br />

Zielregister schreiben)<br />

• Gegenabhängigkeit (ein<br />

überholen<strong>de</strong>r Befehl will schon<br />

ein Da<strong>tu</strong>m än<strong>de</strong>rn, dass noch<br />

zur Berechnung benötigt wird)<br />

• Auflösung: Benutzung von<br />

ver<strong>de</strong>ckten Renaming-<br />

Registern

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

3. Steuerflusskonflikt<br />

• entsteht durch eine verzögerte<br />

Ausführung <strong>de</strong>s Sprungs<br />

• weil das Sprungziel erst noch<br />

berechnet wer<strong>de</strong>n muss (z. B.<br />

relativer Sprung, Branch).<br />

• weil auf die Berechnung <strong>de</strong>r<br />

Sprungbedingung noch gewartet<br />

wer<strong>de</strong>n muss.<br />

• Die Entscheidung zu Auswahl<br />

<strong>de</strong>s nächsten Befehls<br />

wird meist getroffen, bevor das<br />

Sprungziel feststeht, um<br />

Wartezyklen zu vermei<strong>de</strong>n. Es ist<br />

<strong>de</strong>shalb nicht sicher, dass <strong>de</strong>r in die<br />

Pipeline gefütterte Befehl wirklich<br />

als nächster ausgeführt wer<strong>de</strong>n<br />

sollte.<br />

• Auflösung<br />

10–43<br />

• Die Befehle, die hinter <strong>de</strong>m<br />

Sprung stehen (Delayed-<br />

Slot-Befehle) wer<strong>de</strong>n schon<br />

in die Pipeline geholt<br />

• entwe<strong>de</strong>r wer<strong>de</strong>n sie bis<br />

zum En<strong>de</strong> ausgeführt<br />

• o<strong>de</strong>r sie wer<strong>de</strong>n annulliert<br />

(Wirkung: Warten)<br />

• Es wer<strong>de</strong>n die Befehle in die<br />

Pipeline geholt, die entwe<strong>de</strong>r<br />

hinter <strong>de</strong>m Sprung stehen<br />

o<strong>de</strong>r am Sprungziel. Auf<br />

Grund <strong>de</strong>r Vergangenheit<br />

wird <strong>de</strong>r wahrscheinlichere<br />

Weg eingeschlagen<br />

(spekulative Ausführung).

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

<strong>MIPS</strong>: Datenabhängigkeit<br />

10–44<br />

• Beispiel:<br />

sub $2, $1, $3 // 10 -20<br />

and $12, $2, $5 //soll <strong>de</strong>n neuen Wert benutzen<br />

or $13, $6, $2<br />

add $14, $2, $2<br />

sw $15, 100($2)<br />

• sub berechnet $2, wird in <strong>de</strong>n Folgebefehlen<br />

verwen<strong>de</strong>t (gelesen).

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Datenabhängigkeit<br />

Time (in clock cycles)<br />

Value of CC 1 CC 2 CC 3 CC 4 CC 5 CC 6 CC 7 CC 8 CC 9<br />

register $2: 10 10 10 10 10/– 20 – 20 – 20 – 20 – 20<br />

Program<br />

execution<br />

or<strong>de</strong>r<br />

(in instructions)<br />

sub $2, $1, $3<br />

IM<br />

Reg<br />

DM<br />

1.Phase: Write<br />

2.Phase: Read<br />

Reg<br />

10–45<br />

and $12, $2, $5<br />

or $13, $6, $2<br />

IM<br />

inkorrekte<br />

Werte von<br />

$2<br />

Reg<br />

DM Reg<br />

IM Reg DM Reg<br />

add $14, $2, $2<br />

sw $15, 100($2)<br />

korrekte Werte<br />

von $2<br />

IM Reg<br />

DM Reg<br />

IM Reg<br />

DM Reg<br />

• Abhängige Schritte sind durch Pfeile gekennzeichnet.<br />

• Der korrekte Wert von $2 liegt erst nach <strong>de</strong>r 1. Phase (Register<br />

Schreiben) von Zyklus 5 vor.<br />

• Abhängigkeiten, die in <strong>de</strong>r Zeit „rückwärts“ zeigen, sind Datenhür<strong>de</strong>n<br />

(data hazards).

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Datenhür<strong>de</strong>: Software-Lösung<br />

10–46<br />

• Compiler löst bei <strong>de</strong>r Übersetzung in die Maschinensprache<br />

(Assemblersprache) solche Hür<strong>de</strong>n auf.<br />

• z. B. durch Einfügen zweier unabhängiger Operationen:<br />

sub $2, $1, $3<br />

nop<br />

nop<br />

and $12, $2, $5<br />

or $13, $6, $2<br />

add $14, $2, $2<br />

sw $15, 100($2)<br />

• nop (no operation) modifiziert we<strong>de</strong>r Daten noch schreibt<br />

es ein Ergebnis.<br />

• Problem: Bremst das Ganze beträchtlich!<br />

(Und tritt zu häufig auf.)<br />

• Besser: Hardware-Lösung Forwarding

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Datenhür<strong>de</strong>: Vorreichen (Forwarding)<br />

Time (in clock cycles)<br />

CC 1 CC 2 CC 3 CC 4 CC 5 CC 6 CC 7 CC 8 CC 9<br />

Value of register $2 : 10 10 10 10 10/– 20 – 20 – 20 – 20 – 20<br />

Value of EX/MEM : X X X – 20 X X X X X<br />

Value of MEM/WB : X X X X – 20 X X X X<br />

10–47<br />

Program<br />

execution or<strong>de</strong>r<br />

(in instructions)<br />

sub $2, $1, $3<br />

and $12, $2, $5<br />

IM<br />

Reg<br />

IM<br />

Reg<br />

A<br />

EX/MEM<br />

DM<br />

B<br />

MEM/WB<br />

Reg<br />

DM<br />

Reg<br />

vorher ohne Forwarding<br />

mit Forwarding<br />

or $13, $6, $2<br />

add $14, $2, $2<br />

IM Reg DM Reg<br />

C<br />

IM Reg<br />

DM Reg<br />

sw $15, 100($2)<br />

IM Reg<br />

DM Reg<br />

• Direkte Verwendung bereits verfügbarer Zwischenergebnissen von<br />

Pipeline-Registern ohne die Speicherung im Registersatz abzuwarten.<br />

• Vorreichen zur ALU (von EX/MEM bzw. MEM/WB) A, B<br />

• Vorreichen durch Registersatz: Schreiben/Lesen auf gleichem Register im<br />

gleichen Zyklus (z. B. Zyklus 5 im Bild, 1. Phase: Schreiben, 2. Phase: Lesen) C

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Hardware-Erweiterung fürs Vorreichen<br />

ID/EX<br />

EX/MEM<br />

MEM/WB<br />

Load<br />

10–48<br />

Registers<br />

ALU<br />

Data<br />

memory<br />

M ux<br />

ohne Vorreichen<br />

Folgebefehl benutzt<br />

sofort Ergebnis<br />

ID/EX<br />

mit Vorreichen<br />

EX/MEM<br />

MEM/WB<br />

M ux<br />

Registers<br />

ForwardA<br />

ALU<br />

M ux<br />

Data<br />

memory<br />

M ux<br />

Rs<br />

Rt<br />

Rt<br />

Rd<br />

ForwardB<br />

M ux<br />

Forwarding<br />

unit<br />

EX/MEM.RegisterRd<br />

MEM/WB.RegisterRd

Instruction<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Hardware-Erweiterung fürs Vorreichen<br />

10–49<br />

zusätzliche / erweiterte Multiplexer<br />

ID/EX<br />

WB<br />

EX/MEM<br />

Control<br />

M<br />

WB<br />

MEM/WB<br />

IF/ID<br />

EX<br />

M<br />

WB<br />

M<br />

ux<br />

PC<br />

Instruction<br />

memory<br />

Registers<br />

ALU<br />

Data<br />

memory<br />

M<br />

ux<br />

M<br />

ux<br />

IF/ID.RegisterRs<br />

Rs<br />

IF/ID.RegisterRt<br />

Rt<br />

IF/ID.RegisterRt<br />

IF/ID.RegisterRd<br />

Rt<br />

Rd<br />

M<br />

ux<br />

EX/MEM.RegisterRd<br />

Forwarding<br />

unit<br />

MEM/WB.RegisterRd

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Nicht immer kann man vorreichen<br />

Time (in clock cycles)<br />

Program CC 1 CC 2 CC 3 CC 4 CC 5 CC 6<br />

execution<br />

or<strong>de</strong>r<br />

(in instructions)<br />

lw $2, 20($1) IM Reg<br />

DM Reg<br />

10–50<br />

CC 7 CC 8 CC 9<br />

and $4, $2, $5<br />

IM<br />

Reg<br />

DM<br />

Reg<br />

or $8, $2, $6<br />

IM Reg DM Reg<br />

add $9, $4, $2<br />

IM Reg<br />

DM Reg<br />

slt $1, $6, $7<br />

IM Reg<br />

DM Reg<br />

• lw kann immer noch eine Datenhür<strong>de</strong> verursachen.<br />

• Beispiel: Nachfolgen<strong>de</strong>r Befehl versucht, das Register zu lesen, <strong>de</strong>ssen<br />

Wert gera<strong>de</strong> aus <strong>de</strong>m Speicher gela<strong>de</strong>n wird. Das Lesen muss<br />

abgewartet wer<strong>de</strong>n (1 Takt Verzögerung).

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

lw$2, 20($1)<br />

Lösung: Anhalten (Stall)<br />

Program Time(inclock cycles)<br />

execution<br />

or<strong>de</strong>r<br />

(ininstructions)<br />

CC1 CC2 CC3 CC4 CC5 CC6<br />

IM<br />

Reg<br />

DM<br />

Reg<br />

10–51<br />

CC7 CC8 CC9 CC10<br />

and$4, $2, $5<br />

IM<br />

Reg<br />

Reg<br />

DM<br />

Reg<br />

or $8, $2, $6<br />

add$9, $4, $2<br />

IM<br />

IM Reg DM Reg<br />

bubble<br />

IM Reg<br />

DM Reg<br />

slt $1, $6, $7<br />

IM Reg<br />

DM Reg<br />

• Anhalten (stall) <strong>de</strong>r Pipeline durch Belassen <strong>de</strong>s Befehls im gleichen Abschnitt,<br />

d. h. Einfügen eines nop Steuerbefehls ab <strong>de</strong>m EX-Abschnitt (EX, WB, MEM-<br />

Steuersignale auf 0).<br />

• Verhin<strong>de</strong>rn, dass PC fortgeschrieben und das ID-Register geän<strong>de</strong>rt wird.

Instruction<br />

IF/IDWrite<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Anhalten <strong>de</strong>r Pipeline<br />

10–52<br />

• Es wird eine Hazard Detection Unit benötigt, um <strong>de</strong>n Folgebefehl rechtzeitig<br />

„aufzuhalten“. Sie erkennt die Befehlsfolge (lw $2.. , and .. $2 ..)<br />

1 Takt warten<br />

and<br />

Hazard<br />

<strong>de</strong>tection<br />

unit<br />

lw<br />

ID/EX.MemRead<br />

ID/EX<br />

WB<br />

EX/MEM<br />

IF/ID<br />

Control<br />

0<br />

M<br />

ux<br />

M<br />

EX<br />

WB<br />

M<br />

MEM/WB<br />

WB<br />

PCWrite<br />

M<br />

ux<br />

PC<br />

Instruction<br />

memory<br />

Registers<br />

ALU<br />

Data<br />

memory<br />

M<br />

ux<br />

M<br />

ux<br />

M<br />

ux<br />

IF/ID.RegisterRs<br />

IF/ID.RegisterRt<br />

IF/ID.RegisterRt<br />

IF/ID.RegisterRd<br />

Rt<br />

Rd<br />

EX/MEM.RegisterRd<br />

ID/EX.RegisterRt<br />

$2<br />

Rs<br />

Rt<br />

Forwarding<br />

unit<br />

MEM/WB.RegisterRd

Instruction<br />

MemWrite<br />

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

<strong>MIPS</strong>: Steuerflusskonflikt<br />

10–53<br />

PCSrc<br />

Sprungziel<br />

M ux<br />

0<br />

1<br />

2. S<strong>tu</strong>fe<br />

Control<br />

ID/EX<br />

WB<br />

M<br />

EX/MEM<br />

WB<br />

4. S<strong>tu</strong>fe<br />

MEM/WB<br />

IF/ID<br />

EX<br />

M<br />

WB<br />

4<br />

Add<br />

Problem: Sprungziel ist erst in <strong>de</strong>r 4.<br />

Read<br />

S<strong>tu</strong>fe bekannt. PC Address 3 Delayed-Slot-Befehle<br />

register1 Read<br />

Read data1<br />

Instruction<br />

register2<br />

befin<strong>de</strong>n sich schon<br />

memory<br />

in <strong>de</strong>r Pipeline. Registers<br />

Write<br />

Read<br />

register<br />

data2<br />

Write<br />

data<br />

• 1. Lösung:<br />

• Anhalten (stall) bis Sprungziel ermittelt,<br />

Instruction<br />

[15–0] 16 32<br />

Sign<br />

extend<br />

Instruction<br />

• Annahme: kein Sprung (Branch [20–16] not<br />

• 2. Lösung:<br />

taken), Folgebefehle (Delayed-<br />

Instruction<br />

[15–11]<br />

Slot-Befehle) starten<br />

• Falls nachträglich<br />

Sprungbedingung=true erkannt<br />

wird: DS-Befehle ignorieren<br />

RegWrite<br />

Add result<br />

Add<br />

Shift<br />

left 2<br />

• 3. Lösung:<br />

ALUSrc<br />

M ux<br />

0<br />

0<br />

M ux<br />

1<br />

6<br />

1<br />

RegDst<br />

ALUOp<br />

Branch<br />

• Dynamische Zero Sprungvorhersage<br />

ALU ALU<br />

anhand result <strong>de</strong>r Vergangenheit<br />

• 4. Lösung:<br />

Address<br />

Data<br />

memory<br />

Write<br />

data<br />

Read<br />

data<br />

• Sprungzielberechnung von 4.<br />

ALU<br />

control<br />

MemRead<br />

S<strong>tu</strong>fe auf 2. S<strong>tu</strong>fe vorziehen<br />

MemtoReg<br />

M ux<br />

1<br />

0

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Steuerflusskonflikt bei bedingter Verzweigung (1)<br />

10–54<br />

Program<br />

execution<br />

or<strong>de</strong>r<br />

(in instructions)<br />

Time (in clock cycles)<br />

CC 1<br />

CC 2 CC 3 CC 4 CC 5 CC 6 CC 7 CC 8 CC 9<br />

40 beq $1, $3, 7<br />

IM<br />

Reg<br />

DM<br />

Reg<br />

44 and $12, $2, $5<br />

+1<br />

IM<br />

Reg<br />

DM<br />

Reg<br />

48 or $13, $6, $2<br />

+1<br />

IM<br />

Reg<br />

DM<br />

Reg<br />

52 add $14, $2, $2<br />

Delayed-Slot-<br />

Befehle<br />

+1<br />

IM<br />

Reg<br />

DM<br />

Reg<br />

72 lw $4, 50($7)<br />

Sprungziel erst<br />

nach 3 Takten bekannt<br />

+1<br />

?<br />

IM<br />

Reg<br />

DM<br />

Reg<br />

• Problem: 3 Delayed-Slot-Befehle befin<strong>de</strong>n sich schon in <strong>de</strong>r Pipeline.<br />

• 1. Lösung: Anhalten (Beispiel: 3 Anhalte-(stall)-Zyklen) bis Sprungziel ermittelt,<br />

um die Ausführung <strong>de</strong>r Delayed-Slot-Befehle zu verhin<strong>de</strong>rn!

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Steuerflusskonflikt bei bedingter Verzweigung (2)<br />

10–55<br />

not<br />

taken<br />

40 beq $1, $3, 7<br />

44 and $12, $2, $5<br />

48 or $13, $6, $2<br />

52 add $14, $2, $2<br />

72 lw $4, 50($7)<br />

taken<br />

Delayed-Slot-<br />

Befehle<br />

• 2. Lösung:<br />

Annahme kein Sprung (Branch not<br />

taken), Folgebefehle (Delayed-Slot-<br />

Befehle) starten;<br />

bei nachträglicher Erkennung eines<br />

Sprunges (taken) <br />

• (a) DS-Befehle regulär been<strong>de</strong>n. Die<br />

Delayed-Slot-Befehle wer<strong>de</strong>n immer<br />

ausgeführt und können ggf. eine<br />

sinnvolle Berechnung (unabh. vom<br />

Sprung durchführen). Auffüllung mit<br />

nops, falls keine sinnvollen Aktionen<br />

möglich.<br />

• o<strong>de</strong>r (b) <strong>de</strong>r alte Zustand vor <strong>de</strong>m<br />

Sprung wird restauriert. Wirkung <strong>de</strong>r DS-<br />

Befehle rückgängig machen.

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Steuerflusskonflikt bei bedingter Verzweigung (3)<br />

10–56<br />

40 beq $1, $3, 7<br />

Vorhersage<br />

44 and $12, $2, $5<br />

48 or $13, $6, $2<br />

52 add $14, $2, $2<br />

Delayed-Slot-<br />

Befehle<br />

• 3. Lösung: Der dynamischen<br />

Programmablaufs wird verfolgt und die<br />

Sprünge in <strong>de</strong>r Vergangenheit wer<strong>de</strong>n<br />

aufgezeichnet. Aus dieser Information wird<br />

eine Sprungvorhersage getroffen. Dadurch<br />

wird mit hoher Wahrscheinlichkeit <strong>de</strong>r<br />

richtige Weg eingeschlagen.<br />

72 lw $4, 50($7)

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Steuerung mit Verkürzung <strong>de</strong>r Verzweigung<br />

10–57<br />

• 4. Lösung: Sprungzielberechnung von 4. S<strong>tu</strong>fe auf 2. S<strong>tu</strong>fe vorziehen und<br />

Hardware zum Löschen (flush) <strong>de</strong>s bereits geholten Befehls (steht vor <strong>de</strong>m IF/ID-<br />

Register) durch Überschreiben mit NOPs.<br />

IF.Flush<br />

Unbedingtem Sprung:<br />

Sprungziel bekannt<br />

1 nop bubble<br />

IF/ID<br />

Hazard<br />

<strong>de</strong>tection<br />

unit<br />

Control<br />

Sprungbedingung wird schon in <strong>de</strong>r<br />

Decodierphase ausgewertet<br />

(Vergleicher)<br />

1 nop bubble<br />

0<br />

Bedingter Sprung<br />

ID/EX<br />

WB<br />

M ux M<br />

EX<br />

Bedingter Sprung<br />

Vorgänger-Befehl än<strong>de</strong>rt einen<br />

Vergleichsoperan<strong>de</strong>n,auf <strong>de</strong>n gewartet<br />

wer<strong>de</strong>n muss.<br />

2 nop bubbles<br />

EX/MEM<br />

WB<br />

M<br />

MEM/WB<br />

WB<br />

4<br />

M ux<br />

PC<br />

Instruction<br />

memory<br />

M ux<br />

=<br />

Shift<br />

left 2<br />

Registers<br />

ALU<br />

Data<br />

memory<br />

M ux<br />

M ux<br />

M ux<br />

Sign<br />

extend<br />

NOP<br />

Forwarding<br />

unit

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Weitere Leis<strong>tu</strong>ngssteigerung (1)<br />

• Compiler: Vermei<strong>de</strong>n <strong>de</strong>s Anhaltens <strong>de</strong>r Pipeline von Compilerseite durch<br />

Umordnung von Befehlen (Lösung 2 a)<br />

• Superpipelining: Längere Fließbän<strong>de</strong>r mit 8 und mehr S<strong>tu</strong>fen<br />

• Superskalare Prozessoren:<br />

• In je<strong>de</strong>m Taktzyklus Start mehrerer Befehle gleichzeitig (z. B. 2 bis 8).<br />

• Voraussetzung: Zusätzliche Hardware-Einheiten notwendig zur Vermeidung<br />

von Ressourcenkonflikten. Z. B. Start zweier ALU-Operationen erfor<strong>de</strong>rt zwei<br />

ALUs.<br />

• z. B. superskalare Version von <strong>MIPS</strong><br />

• Gleichzeitig eine ALU- o<strong>de</strong>r Verzweigung sowie eine La<strong>de</strong>- o<strong>de</strong>r<br />

Speicheroperation aktivierbar.<br />

• In einem 64 Bit Befehlsregister können zwei aufeinan<strong>de</strong>r folgen<strong>de</strong> Befehle<br />

gepuffert und dann parallel <strong>de</strong>codiert wer<strong>de</strong>n.<br />

10–58

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Weitere Leis<strong>tu</strong>ngssteigerung (2)<br />

10–59<br />

Dynamisches Pipelining (dynamic pipeline scheduling):<br />

• Hardware zum Aufspüren und Abarbeiten unabhängiger Befehle<br />

• in-or<strong>de</strong>r issue: Befehle wer<strong>de</strong>n in Programmordnung aktiviert<br />

• out-of-or<strong>de</strong>r execution: Ausführung in unabhängigen funktionalen Einheiten<br />

mit Befehlspuffern (reservation stations) und Ergebnispuffern<br />

• in-or<strong>de</strong>r commit: fertig bearbeitete Befehle wer<strong>de</strong>n wie<strong>de</strong>r in die<br />

Programmreihenfolge gebracht (Schreiben in die Architek<strong>tu</strong>r-Register o<strong>de</strong>r<br />

Speicher).<br />

Instruction fetch<br />

and <strong>de</strong>co<strong>de</strong> unit<br />

In-or<strong>de</strong>r issue<br />

Reservation<br />

station<br />

Reservation<br />

station<br />

…<br />

Reservation<br />

station<br />

Reservation<br />

station<br />

Functional<br />

units<br />

Integer<br />

Integer<br />

…<br />

Floating<br />

point<br />

Load/<br />

Store<br />

Out-of-or<strong>de</strong>r execute<br />

Commit<br />

unit<br />

In-or<strong>de</strong>r commit

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Aus <strong>de</strong>r Technik<br />

10–60<br />

• Alle mo<strong>de</strong>rnen Prozessoren sind äußerst komplex.<br />

• Compaq/DEC Alpha 21264:<br />

• 9-s<strong>tu</strong>fige Pipeline, 6 Befehle gleichzeitig<br />

• Intel/HP Itanium:<br />

• bis zu 6 IA-64-Befehle gleichzeitig<br />

• DEC Alpha 21164, PowerPC G3, <strong>MIPS</strong> R12000, UltraSparc-<br />

II, HP PA-8500:<br />

• bis zu 4 Befehle pro Takt<br />

• PowerPC, Pentium:<br />

• Sprungvorhersage-Tabelle<br />

• Trace-Cache: Befehlsgruppen wer<strong>de</strong>n dynamisch in Mikrobefehle<br />

zur Laufzeit übersetzt. Bei erneuter Ausführung wer<strong>de</strong>n die<br />

Mikrobefehle benutzt.<br />

• Ak<strong>tu</strong>elle Prozessortechnik siehe Kap. 12, Multicores,<br />

Manycores

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Zusammenfassung <strong>Teil</strong> 2<br />

10–61<br />

• Konflikte<br />

• Ressourcen-Konflikt Bubbles<br />

• Datenkonflikte Bubbles, Forwarding<br />

• Steuerflusskonflikt<br />

• Abwarten bis Sprungbedingung und Sprungziel berechnet<br />

• Delayed-Slot-Befehle befin<strong>de</strong>n sich in <strong>de</strong>r Pipeline<br />

• Auflösung <br />

• Software NOPs<br />

• Stall (Bubbles)<br />

• Forwarding<br />

• Sprungvorhersage

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

Ergänzung: lw add mit Datenabhängigkeit<br />

10–62 2<br />

lw

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

10–63 3<br />

lw<br />

Reg<br />

read<br />

and

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

10–64 4<br />

lw<br />

Reg<br />

read<br />

ALU<br />

and<br />

Reg<br />

read<br />

Hazard<br />

Detect

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

10–65 5<br />

lw<br />

Reg<br />

read<br />

ALU<br />

M<br />

read<br />

and<br />

Reg<br />

read<br />

Reg<br />

read<br />

bubble<br />

Hazard<br />

Detect

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

10–66 6<br />

lw<br />

Reg<br />

read<br />

ALU<br />

M<br />

read<br />

Reg<br />

write<br />

and<br />

Reg<br />

read<br />

Reg<br />

read<br />

ALU<br />

Hazard<br />

Detect

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

10–67 7<br />

lw<br />

Reg<br />

read<br />

ALU<br />

M<br />

read<br />

Reg<br />

write<br />

and<br />

Reg<br />

read<br />

Reg<br />

read<br />

ALU<br />

Hazard<br />

Detect

<strong>Technische</strong> Grundlagen <strong>de</strong>r Informatik 2, SS 09, R. Hoffmann, TUD<br />

10–68 8<br />

lw<br />

Reg<br />

read<br />

ALU<br />

M<br />

read<br />

Reg<br />

write<br />

and<br />

Reg<br />

read<br />

Reg<br />

read<br />

ALU<br />

Reg<br />

write<br />

Hazard<br />

Detect