Vorlesungsfolien Termin 8

Vorlesungsfolien Termin 8

Vorlesungsfolien Termin 8

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

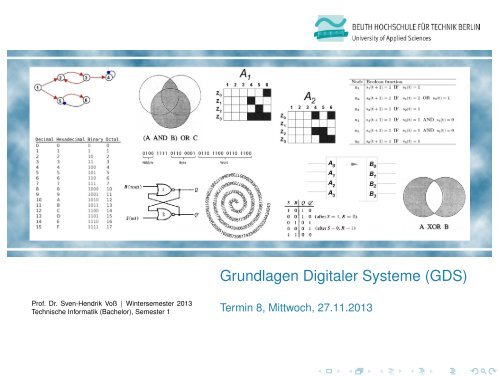

Grundlagen Digitaler Systeme (GDS)<br />

Prof. Dr. Sven-Hendrik Voß | Wintersemester 2013<br />

Technische Informatik (Bachelor), Semester 1 <strong>Termin</strong> 8, Mittwoch, 27.11.2013

Seite 2 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Inhaltsverzeichnis<br />

Themen und <strong>Termin</strong>e<br />

Lernziele<br />

Logische Grundschaltungen<br />

Halbaddierer<br />

Volladdierer<br />

Mehrstellige Addierer<br />

Subtrahierer<br />

Zusammenfassung

Seite 3 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Themen und <strong>Termin</strong>e - Seminaristischer Unterricht<br />

Seminaristischer Unterricht (SU) im Raum B321, mittwochs 10:00 - 11:30 Uhr<br />

Nr. Datum Themen Kurztest<br />

1 09.10. Einführung; Boolesche Algebra (1)<br />

2 16.10. Boolesche Algebra (2)<br />

3 23.10. Vereinfachung logischer Funktionen (1)<br />

4 30.10. Vereinfachung logischer Funktionen (2)<br />

5 06.11. Zahlensysteme (1)<br />

6 13.11. Zahlensysteme (2) 1<br />

7 20.11. Logische Grundschaltungen (1)<br />

8 27.11. Logische Grundschaltungen (2)<br />

9 04.12. Binär-Codes (1)<br />

10 11.12. Binär-Codes (2) 2<br />

11 18.12. Sequentielle Logik (1)<br />

25.12. Weihnachtsferien<br />

01.01. Weihnachtsferien<br />

12 08.01. Sequentielle Logik (2)<br />

13 15.01. Sequentielle Logik (3)<br />

14 22.01. Busse, Entwicklung Addierwerk 3<br />

15 29.01. Sequentielle Logik (4)<br />

16 05.02. Klausur<br />

17 12.02. Klausurrückgabe und -besprechung

Seite 4 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Lernziele<br />

Nach diesem <strong>Termin</strong> sollten Sie...<br />

◮<br />

◮<br />

◮<br />

◮<br />

Addierschaltungen als weitere Vertreter häufig verwendeter<br />

Datenpfadkomponenten kennengelernt haben<br />

den Unterschied zwischen Halbaddierer und Volladdierer verstanden<br />

haben<br />

den Aufbau, sowie Vor- und Nachteile von Ripple-Carry- und<br />

Carry-Lookahead-Addierern kennen<br />

einen Subtrahierer aus einem Addierer ableitern können

Seite 5 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Logische Grundschaltungen<br />

Alle Grundrechenarten lassen sich auf die Addition zurückführen.<br />

◮<br />

◮<br />

◮<br />

Subtraktion<br />

Multiplikation<br />

Division<br />

→ Addierer: Grundschaltung für alle arithmetischen Operationen

Seite 6 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Halbaddierer<br />

Der Halbaddierer addiert zwei Bit<br />

und stellt im Fall der Addition von<br />

1 + 1 ein Übertragsbit (Carry Bit)<br />

zur Verfügung<br />

Schaltsymbol<br />

a<br />

s<br />

Wahrheitstabelle<br />

b a s c<br />

0 0 0 0<br />

0 1 1 0<br />

1 0 1 0<br />

1 1 0 1<br />

b<br />

Schaltfunktionen für Summe und Carry-Bit<br />

s = (a · b) + (a · b) = a ⊕ b<br />

c = a · b<br />

c

Seite 7 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Volladdierer<br />

Den Volladdierer erhält man durch<br />

Zusammenschaltung von zwei<br />

Halbaddierern<br />

◮<br />

Übertrag des ersten Halbaddierers<br />

als Eingangsgröße<br />

für die zweite XOR-<br />

Verknüpfung verwendet<br />

Wahrheitstabelle<br />

c i−1 b i a i s i c i a i ⊕ b i<br />

0 0 0 0 0 0<br />

0 0 1 1 0 1<br />

0 1 0 1 0 1<br />

0 1 1 0 1 0<br />

1 0 0 1 0 0<br />

1 0 1 0 1 1<br />

1 1 0 0 1 1<br />

1 1 1 1 1 0<br />

Schaltsymbol<br />

a i<br />

b i<br />

c i-1<br />

Kaskadierung der zwei XOR-Gatter zur<br />

Realisierung der Funktion s i<br />

a i<br />

=1<br />

b i =1<br />

c i-1<br />

s i<br />

c i<br />

s i

Seite 8 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Volladdierer<br />

Mögliche Realisierung eines Volladdierers für zwei Bit<br />

a i<br />

b i<br />

=1<br />

=1<br />

s i<br />

&<br />

&<br />

>=1<br />

c i<br />

c i-1<br />

G i<br />

P i<br />

Im wesentlichen: zwei Halbaddierer (zzgl. OR-Gatter)<br />

Ausgangssignale G i und P i relevant für Addierer mit Parallelübertrag<br />

(Carry-Lookahead Generator)

Seite 9 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Mehrstellige Addierer<br />

Schaltung eines 4-Bit-Addierers mit seriellem Übertrag<br />

a 0<br />

b 0 a 1<br />

c 0<br />

s 1<br />

b 1 a 2<br />

c 1<br />

s 2<br />

b 2 a 3<br />

c 2<br />

s 3<br />

b 3<br />

c 3<br />

0 = c -1<br />

s 0<br />

Addition der vierstelligen Binärzahlen<br />

a = a 0 + a 1 2 + a 2 2 2 + a 3 2 3 und b = b 0 + b 1 2 + b 2 2 2 + b 3 2 3<br />

durch Zusammenschaltung von vier Halbaddierern<br />

◮<br />

◮<br />

für i Stellen: i Volladdierer oder i-1 Volladdierer und 1 Halbaddierer<br />

Ergebnis maximal (i+1)-stellig<br />

→ kaskadierbares Addierwerk, mit dem man i-stellige Addierwerke<br />

bauen kann (Ripple-Carry-Addierer mit Übertragsdurchlauf)

Seite 10 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Mehrstellige Addierer<br />

Serienübertrag: Durchschleifen der Carry-Signale von der niedrigsten bis zur<br />

höchsten Stelle bedingt lange Laufzeiten<br />

Abhilfe: aufwendigeres Carry-Lookahead Prinzip<br />

Parallele Erzeugung der Überträge für alle Binärstellen der Summanden aus<br />

◮<br />

◮<br />

weitergereichtem ( ”<br />

propagated“) Übertrag: P i = a i ⊕ b i<br />

generiertem ( ”<br />

generated“) Übertrag: G i = a i · b i<br />

Anwendung auf Summen- und Carry-Berechnung<br />

c i = (a i · b i ) + c i−1 · (a i ⊕ b i ) = G i + c i−1 · P i<br />

s i = (a i ⊕ b i ) ⊕ c i−1 = P i ⊕ c i−1

Seite 11 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Mehrstellige Addierer<br />

Für das Beispiel der vierstelligen Binärzahlen (c −1 = 0)<br />

c 0 = G 0<br />

c 1 = G 1 + P 1 · c 0 = G 1 + P 1 · G 0<br />

c 2 = G 2 + P 2 · c 1 = G 2 + P 2 · G 1 + P 2 · P 1 · G 0<br />

c 3 = G 3 + P 3 · c 2 = G 3 + P 3 · G 2 + P 3 · P 2 · G 1 + P 3 · P 2 · P 1 · G 0<br />

→<br />

Übertragsgenerator (Schaltnetz) zur Bildung der Carry-Signale als<br />

kombinatorische Schaltfunktionen der Eingangssignale aller Stellen

Seite 12 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Mehrstellige Addierer<br />

Addierer mit Übertrags-Generator (Carry-Lookahead Generator)<br />

s0<br />

s1<br />

s2<br />

s3<br />

a0<br />

b0<br />

a1<br />

b1<br />

a2<br />

b2<br />

a3<br />

b3<br />

c0<br />

c1<br />

c2<br />

0 = c-1<br />

G0<br />

P0<br />

G1 P1<br />

G2 P2<br />

G3 P3<br />

G0<br />

CPG<br />

G1<br />

G2<br />

G3<br />

P0<br />

P1<br />

P2<br />

c0<br />

c1<br />

c2<br />

c3<br />

P3

Seite 13 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Subtrahierer<br />

Erweiterung des Addierwerks zum Addier-/Subtrahierwerk<br />

m<br />

b0<br />

=1<br />

b1<br />

=1<br />

b2<br />

=1<br />

b3<br />

=1<br />

a0<br />

a1<br />

a2<br />

a3<br />

c-1<br />

c0<br />

c1<br />

c2<br />

c3<br />

mit m: Modusbit<br />

s0<br />

s1<br />

s2<br />

s3<br />

◮<br />

◮<br />

= 1 → XOR invertiert das Eingangssignal und setzt das Carry-In Bit,<br />

hierdurch entsteht das Zweierkomplement und aus der Addition wird<br />

eine Subtraktion<br />

= 0 → XOR verändert das Eingangssignal nicht, normale Addition

Seite 14 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Subtrahierer<br />

Subtraktion durch Vorzeichenwechsel des Subtrahenden als Addition<br />

durchführbar<br />

◮<br />

◮<br />

Vorzeichenwechsel durch Zweierkomplement (Invertierung aller Bits und<br />

anschließende Addition mit 1)<br />

Invertierung durch Vorschaltung von XOR-Verknüpfungen am Eingang<br />

des zweiten Operanden<br />

◮ Addition von 1 durch Setzen des Carry-In (c −1 )

Seite 15 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Zusammenfassung<br />

Heute haben Sie gelernt...<br />

◮<br />

◮<br />

◮<br />

◮<br />

was ein Halb- und Volladdierer ist<br />

wie man mehrstellige Addierer baut<br />

welche Optimierungsmöglichkeiten von Addierschaltungen es gibt<br />

wie sich eine Subtraktion aus einem Addierer ableiten lässt

Seite 16 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Ausblick auf nächste Stunde<br />

In der nächsten Stunde widmen wir uns...<br />

◮<br />

◮<br />

digitalen Darstellungen, insbesondere numerischen Codes<br />

der Anwendung solcher Codes

Seite 17 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Hinweise zum Selbststudium<br />

Zur Vertiefung wird empfohlen...<br />

◮<br />

GDS-Skript<br />

◮ Pernards: Digitaltechnik Band 1, Hüthig Verlag, ISBN 3778528157

Seite 18 Logische Grundschaltungen | Grundlagen digitaler Systeme | Wintersemester 2013<br />

Kritik<br />

Nun sind Sie dran:<br />

◮<br />

◮<br />

◮<br />

◮<br />

Kritik: Was funktioniert gut / was schlecht?<br />

Anregungen<br />

Wünsche<br />

Verbesserungsvorschläge in Bezug auf Inhalt und Organisation der<br />

Vorlesung