Physical Model of a Banjo in FPGA Design - Systmuwi.de

Physical Model of a Banjo in FPGA Design - Systmuwi.de Physical Model of a Banjo in FPGA Design - Systmuwi.de

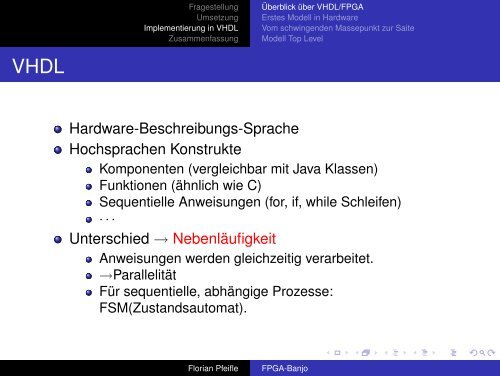

Fragestellung Umsetzung Implementierung in VHDL Zusammenfassung Überblick über VHDL/FPGA Erstes Modell in Hardware Vom schwingenden Massepunkt zur Saite Modell Top Level VHDL Hardware-Beschreibungs-Sprache Hochsprachen Konstrukte Komponenten (vergleichbar mit Java Klassen) Funktionen (ähnlich wie C) Sequentielle Anweisungen (for, if, while Schleifen) · · · Unterschied → Nebenläufigkeit Anweisungen werden gleichzeitig verarbeitet. →Parallelität Für sequentielle, abhängige Prozesse: FSM(Zustandsautomat). Florian Pfeifle FPGA-Banjo

Fragestellung Umsetzung Implementierung in VHDL Zusammenfassung Überblick über VHDL/FPGA Erstes Modell in Hardware Vom schwingenden Massepunkt zur Saite Modell Top Level VHDL Hardware-Beschreibungs-Sprache Hochsprachen Konstrukte Komponenten (vergleichbar mit Java Klassen) Funktionen (ähnlich wie C) Sequentielle Anweisungen (for, if, while Schleifen) · · · Unterschied → Nebenläufigkeit Anweisungen werden gleichzeitig verarbeitet. →Parallelität Für sequentielle, abhängige Prozesse: FSM(Zustandsautomat). Florian Pfeifle FPGA-Banjo

- Seite 1 und 2: Fragestellung Umsetzung Implementie

- Seite 3 und 4: Überblick Fragestellung Umsetzung

- Seite 5 und 6: Fragestellung Umsetzung Implementie

- Seite 7 und 8: Fragestellung Umsetzung Implementie

- Seite 9 und 10: Fragestellung Umsetzung Implementie

- Seite 11 und 12: Überblick Fragestellung Umsetzung

- Seite 13 und 14: Finite Differenzen Fragestellung Um

- Seite 15 und 16: Finite Differenzen Fragestellung Um

- Seite 17 und 18: Finite Differenzen Fragestellung Um

- Seite 19 und 20: Finite Differenzen Fragestellung Um

- Seite 21 und 22: Fragestellung Umsetzung Implementie

- Seite 23 und 24: Umsetzung Fragestellung Umsetzung I

- Seite 25 und 26: Umsetzung Fragestellung Umsetzung I

- Seite 27 und 28: Fragestellung Umsetzung Implementie

- Seite 29 und 30: Fragestellung Umsetzung Implementie

- Seite 31 und 32: Fragestellung Umsetzung Implementie

- Seite 33 und 34: Überblick Fragestellung Umsetzung

- Seite 35 und 36: Fragestellung Umsetzung Implementie

- Seite 37: Fragestellung Umsetzung Implementie

- Seite 41 und 42: Fragestellung Umsetzung Implementie

- Seite 43 und 44: Fragestellung Umsetzung Implementie

- Seite 45 und 46: Fragestellung Umsetzung Implementie

- Seite 47 und 48: Fragestellung Umsetzung Implementie

- Seite 49 und 50: Fragestellung Umsetzung Implementie

- Seite 51 und 52: Fragestellung Umsetzung Implementie

- Seite 53 und 54: Fragestellung Umsetzung Implementie

- Seite 55 und 56: Fragestellung Umsetzung Implementie

- Seite 57 und 58: Fragestellung Umsetzung Implementie

- Seite 59: Fragestellung Umsetzung Implementie

Fragestellung<br />

Umsetzung<br />

Implementierung <strong>in</strong> VHDL<br />

Zusammenfassung<br />

Überblick über VHDL/<strong>FPGA</strong><br />

Erstes <strong>Mo<strong>de</strong>l</strong>l <strong>in</strong> Hardware<br />

Vom schw<strong>in</strong>gen<strong>de</strong>n Massepunkt zur Saite<br />

<strong>Mo<strong>de</strong>l</strong>l Top Level<br />

VHDL<br />

Hardware-Beschreibungs-Sprache<br />

Hochsprachen Konstrukte<br />

Komponenten (vergleichbar mit Java Klassen)<br />

Funktionen (ähnlich wie C)<br />

Sequentielle Anweisungen (for, if, while Schleifen)<br />

· · ·<br />

Unterschied → Nebenläufigkeit<br />

Anweisungen wer<strong>de</strong>n gleichzeitig verarbeitet.<br />

→Parallelität<br />

Für sequentielle, abhängige Prozesse:<br />

FSM(Zustandsautomat).<br />

Florian Pfeifle<br />

<strong>FPGA</strong>-<strong>Banjo</strong>