Prüfung - Institut für Kommunikationsnetze und Rechnersysteme ...

Prüfung - Institut für Kommunikationsnetze und Rechnersysteme ...

Prüfung - Institut für Kommunikationsnetze und Rechnersysteme ...

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Universität Stuttgart<br />

INSTITUT FÜR<br />

KOMMUNIKATIONSNETZE<br />

UND RECHNERSYSTEME<br />

Prof. Dr.-Ing. Andreas Kirstädter<br />

Diplomprüfung<br />

Prüfer:<br />

Termin:<br />

Dauer:<br />

Verlangte Aufgaben:<br />

Zugelassene Hilfsmittel:<br />

Entwurf digitaler Systeme<br />

Kirstädter, Meyer<br />

15. Oktober 2010<br />

90 Minuten<br />

alle<br />

alle<br />

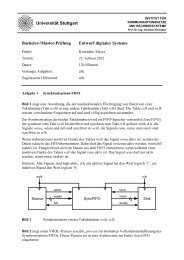

Aufgabe 1<br />

CRC-Berechnung<br />

Bild 1 zeigt ein sogenanntes rückgekoppeltes Schieberegister zur Berechnung einer Prüfsumme<br />

("Cyclic Red<strong>und</strong>ancy Check", CRC). Mit Hilfe einer solchen Prüfsumme ist es möglich, Bitfehler<br />

in einem Nachrichtenblock (z.B. in einem Datenpaket im Internet) zu erkennen oder<br />

sogar zu korrigieren.<br />

=1<br />

=1<br />

=1<br />

m<br />

clk<br />

clr<br />

q(7)<br />

q(6)<br />

q(5)<br />

q(4)<br />

q(3)<br />

q(2)<br />

q(1)<br />

q(0)<br />

Bild 1<br />

Rückgekoppeltes Schieberegister<br />

Die Schnittstelle des rückgekoppelten Schieberegisters weist neben dem Takteingang clk<br />

einen Dateneingang m, einen synchronen Löscheingang clr <strong>und</strong> acht Ausgänge q(7) bis<br />

q(0) auf. Die Bezeichnung "rückgekoppelt" rührt daher, dass der Ausgang des letzten<br />

Flipflops q(7) über Exklusiv-Oder-Gatter in einen Teil der vorausgehenden Flipflops eingekoppelt<br />

wird (hier: q(2), q(1)<strong>und</strong> q(0)).<br />

Die Schaltung besteht aus acht D-Flipflops mit synchronem Löscheingang <strong>und</strong> aus drei Exklusiv-Oder-Gattern.<br />

Alle Flipflops werden synchron mit einem Takt clk getaktet. Ist clr während<br />

einer positiven Taktflanke logisch "1", so wird das Flipflop unabhängig vom Dateneingang<br />

zurückgesetzt. Beachten Sie, dass die Bauelemente hier horizontal gespiegelt gezeichnet sind,<br />

d.h. ihre Eingänge befinden sich rechts <strong>und</strong> ihre Ausgänge links.

Frage 1 a) Geben Sie eine VHDL-Entity dff <strong>für</strong> das in der Schaltung verwendete<br />

Flipflop mit synchronem Löscheingang an. Bezeichnen Sie den Takteingang<br />

mit clk, den synchronen Löscheingang mit clr, den Dateneingang<br />

mit d <strong>und</strong> den Datenausgang mit q.<br />

b) Geben Sie eine VHDL-Architecture behav <strong>für</strong> die Entity dff in Form<br />

einer vollständigen Verhaltensbeschreibung an.<br />

c) Warum ist es eine schlechte Idee, die Entity im vorliegenden Fall mit<br />

behav zu bezeichnen <strong>und</strong> da<strong>für</strong> die Architecture mit dff?<br />

d) Wie könnte eine Strukturbeschreibung <strong>für</strong> die Entity dff prinzipiell aussehen?<br />

Antworten Sie in wenigen Stichworten <strong>und</strong> geben Sie insbesondere<br />

keinen VHDL-Code an.<br />

Frage 2 a) Geben Sie eine VHDL-Entity crc <strong>für</strong> die Schaltung in Bild 1 an.<br />

b) Setzen Sie den Schaltplan in Bild 1 in eine VHDL-Architecture struct<br />

<strong>für</strong> die Entity crc um.<br />

Hinweise<br />

• Instanziieren Sie das D-Flipflop gemäß Frage 1 acht Mal mit Hilfe der<br />

direkten Instanziierung (d.h. ohne die Deklaration eines Component).<br />

• Verwenden Sie bei der Instanziierung "positional association" (d.h.<br />

Parameterzuordnung durch Position). Beachten Sie dabei, dass als<br />

Parameter nur Signale <strong>und</strong> keine Ausdrücke zulässig sind.<br />

• Modellieren Sie die Exklusiv-Oder-Gatter direkt mit Hilfe des xor-<br />

Operators.<br />

• Deklarieren <strong>und</strong> verwenden Sie geeignete Signale.<br />

c) Geben Sie nun eine Verhaltensbeschreibung in Form einer VHDL-Architecture<br />

behav <strong>für</strong> die Entity crc an.<br />

Hinweise<br />

• Die Architectures struct <strong>und</strong> behav sollen sich an ihrer Schnittstelle<br />

gleich verhalten.<br />

• Verwenden Sie in der Architecture behav nur einen einzigen Prozess.<br />

• Achten Sie auf den Unterschied zwischen Signalen <strong>und</strong> Variablen.<br />

Nun werde die Komponente crc in eine Schaltung eingebettet (Bild 2). Neben der Komponente<br />

crc selbst enthält die Schaltung einen Taktgenerator clkgen <strong>und</strong> eine Komponente<br />

mem_and_ctrl. Die Architecture der Komponente mem_and_ctrl verwendet das<br />

Package ieee.numeric_std <strong>und</strong> enthält nur einen einzelnen Prozess, der in Bild 3 angegeben<br />

ist.<br />

Aufgabe 1 Seite 2

clkgen<br />

crc<br />

clk<br />

clk<br />

q<br />

clk<br />

q<br />

clr<br />

m<br />

clr<br />

m<br />

mem_and_ctrl<br />

Bild 2<br />

Schaltung<br />

01 process is<br />

02<br />

03 type mem_t is array (0 to 255) of std_logic_vector(7 downto 0);<br />

04<br />

05 variable mem: mem_t := (<br />

06 x"02", x"81", x"01", x"00", x"07", x"a6", x"72", x"22",<br />

07 x"f0", x"3b", x"14", x"49", x"00", x"05", x"22", x"15",<br />

08 x"c9", x"ef", x"59", x"00", x"00", others => x"ff");<br />

09<br />

10 variable index, length: integer;<br />

11 variable finish: boolean;<br />

12<br />

13 procedure step is<br />

14 begin<br />

15 wait until clk’event and clk = ’1’;<br />

16 end procedure step;<br />

17<br />

18 begin<br />

19<br />

20 index := 0; finish := false;<br />

21 clr

Frage 3 a) Wie oft wird beim gegebenen Initialwert der Variablen mem die Schleife<br />

main durchlaufen?<br />

b) Geben Sie <strong>für</strong> jeden Schleifendurchlauf der Schleife main an, wie oft die<br />

eingebettete Schleife packet jeweils durchlaufen wird.<br />

c) Wie oft wird die Schleife byte jeweils durchlaufen?<br />

Frage 4 a) Warum wird in Zeile 34 nicht immer der Wert "00000000" in das entsprechende<br />

Element des Arrays mem geschrieben, obwohl das Schieberegister<br />

durch die Sequenz in Zeile 33 gelöscht wird?<br />

b) Welcher Wert wird am Ende des ersten Durchlaufs der Schleife main in<br />

welches Element des Arrays mem geschrieben?<br />

Abschließend soll die Komponente mem_and_ctrl in eine synthetisierbare Form überführt<br />

werden. Dies kann dadurch erfolgen, dass man die Komponente mit Hilfe eines Steuerwerks<br />

ctrl <strong>und</strong> eines Speichers mem implementiert, siehe Bild 4.<br />

clk<br />

mem<br />

ctrl<br />

clk<br />

clk<br />

clr<br />

clr<br />

addr<br />

addr<br />

m<br />

m<br />

q<br />

d_in<br />

d_out<br />

d_out<br />

wr<br />

wr<br />

Bild 4<br />

Strukturbeschreibung <strong>für</strong> die Komponente mem_and_ctrl<br />

Der Speicher mem werde asynchron gelesen <strong>und</strong> synchron beschrieben, d.h. d_out ist eine<br />

kombinatorische Funktion von addr, <strong>und</strong> wenn bei einer positiven Taktflanke wr gleich ’1’<br />

ist, so wird die Speicherstelle an Adresse addr mit d_in überschrieben.<br />

Frage 5<br />

Geben Sie eine vollständige Architecture behav <strong>für</strong> die Komponente mem an.<br />

Hinweise<br />

• Die zugehörige Entity mem ist nicht verlangt.<br />

• Der Speicher muss nicht mit den Daten wie in Bild 3 initialisiert werden.<br />

Der Anfang der Architecture behav <strong>für</strong> die Komponente ctrl ist in Bild 5 angegeben. Die<br />

Implementierung erfolgt mit Hilfe eines Automaten, eines Adresszählers (aufwärts), eines Längenzählers<br />

(abwärts) <strong>und</strong> eines Schieberegisters.<br />

Frage 6<br />

Zeichnen Sie ein Zustandsübergangsdiagramm des Automaten. Beschriften Sie<br />

die Übergänge ggf. mit der Bedingung, die das Eingangssignal jeweils erfüllen<br />

muss. Die Ausgangssignale des Automaten sollen nicht eingezeichnet werden.<br />

Aufgabe 1 Seite 4

library ieee; use ieee.numeric_std.all;<br />

ARCHITECTURE behav OF ctrl IS<br />

signal addr_int: std_logic_vector(7 downto 0);<br />

signal addr_inc, addr_clr: std_logic;<br />

signal counter: std_logic_vector(7 downto 0);<br />

signal counter_load, counter_dec, counter_zero: std_logic;<br />

signal shiftreg: std_logic_vector(7 downto 0);<br />

signal shiftreg_load: std_logic;<br />

type state_type is (<br />

start, load_length, check_length,<br />

shift0, shift1, shift2, shift3, shift4, shift5, shift6,<br />

load_data, store, doom);<br />

signal current_state, next_state: state_type;<br />

BEGIN<br />

process(current_state, counter_zero) is<br />

begin<br />

case current_state is<br />

when start => next_state next_state <br />

if counter_zero = ’1’ then<br />

next_state

Frage 7<br />

Frage 8<br />

Der Automat soll zum Moore-Automaten vervollständigt werden.<br />

a) Welche Ausgangssignale muss der Automat ansteuern?<br />

b) Erzeugen Sie in einem Prozess die Ausgangssignale in Abhängigkeit vom<br />

Zustand des Automaten. Verwenden Sie sinnvolle Default-Zuweisungen <strong>für</strong><br />

die Signale, um Schreibarbeit zu sparen.<br />

Vervollständigen Sie die Architecture behav der Komponente ctrl. Versuchen<br />

Sie dabei, ohne zusätzliche Signal-, Typ- oder Variablendeklarationen auszukommen.<br />

Aufgabe 1 Seite 6

Aufgabe 2<br />

Content-Addressable Memory<br />

Content-Addressable Memories (CAMs) sind inhaltsadressierte Speicher, die immer dann<br />

verwendet werden, wenn in Hardware eine schnelle parallele Suche realisiert werden soll.<br />

Bei einem normalen, ortsadressierten Speicher legt man die Adresse des Orts an den Speicher<br />

an <strong>und</strong> erhält das Datum an diesem Ort. Bei einem inhaltsadressierten Speicher dagegen legt<br />

man den (gesuchten) Inhalt ("Suchschlüssel", "key") an den Speicher an <strong>und</strong> erhält den Ort, an<br />

dem dieser Inhalt im Speicher liegt.<br />

Bild 1 zeigt die Belegung eines kleinen Beispiel-CAM. Eine CAM-Zeile enthält neben dem<br />

Datum data ein Valid-Bit v, das mit v=’1’ die Gültigkeit des Datums anzeigt.<br />

Beispiel: Wird nach dem Datum $080A gesucht, so liefert der CAM im Bild die Adresse 1<br />

als Ergebnis.<br />

address<br />

0<br />

1<br />

2<br />

3<br />

data v<br />

$15FF 1<br />

$080A 1<br />

$1284 0<br />

$4801 1<br />

Bild 1<br />

Frage 1<br />

CAM-Speichermatrix mit vier Zeilen<br />

Aus welchem Gr<strong>und</strong> werden die Valid-Bits überhaupt benötigt?<br />

Bild 2 zeigt die Schnittstelle eines CAM <strong>für</strong> Lese- bzw. Suchzugriffe. Das Schreiben eines<br />

CAM wird im Rahmen dieser Aufgabe nicht betrachtet.<br />

key<br />

KEY_WIDTH<br />

CAM<br />

addr<br />

ADDR_WIDTH<br />

hit<br />

Bild 2<br />

Frage 2<br />

CAM-Schnittstelle<br />

Geben Sie eine VHDL-Entity cam an, die die in Bild 2 gezeigte Schnittstelle<br />

des CAM beschreibt. Mittels zweier generischer Parameter der Entity sollen <strong>für</strong><br />

key <strong>und</strong> addr beliebige Bitbreiten möglich sein. KEY_WIDTH soll dabei die<br />

Schlüsselbreite <strong>und</strong> ADDR_WIDTH die Adressbreite in Bit definieren.<br />

Aufgabe 2 Seite 7

Nun werde eine Architecture behav zur Entity cam betrachtet.<br />

Um die Lesbarkeit <strong>und</strong> Anpassbarkeit der Implementierung zu erhöhen, sollen zunächst diverse<br />

Datentypen definiert werden, die nur innerhalb der Architecture genutzt werden.<br />

Frage 3 a) Wo sollten diese Typen deklariert werden?<br />

b) Deklarieren Sie einen Typ zur Modellierung von Datenworten (data_t).<br />

c) Deklarieren Sie einen problemangepassten Typ line_t, der eine komplette<br />

CAM-Zeile entsprechend Bild 1 modelliert.<br />

d) Deklarieren Sie eine Konstante DEPTH, die die Speichertiefe in Abhängigkeit<br />

der Adressbreite ADDR_WIDTH angibt.<br />

e) Deklarieren Sie einen von DEPTH abhängigen Typ MATRIX_RANGE, der<br />

den Adressbereich des CAM modelliert.<br />

f) Deklarieren Sie nun einen Typ matrix_t zur Modellierung der vollständigen<br />

Speichermatrix des CAM entsprechend Bild 1.<br />

g) Geben Sie die Deklaration eines Signals matrix vom Typ matrix_t an.<br />

Der CAM soll in Form einer Verhaltensbeschreibung modelliert werden. Diese Verhaltensbeschreibung<br />

soll mit einem einzigen Prozess auskommen, der eine sequenzielle Suche modelliert.<br />

Die Verhaltensbeschreibung muss nicht synthetisierbar sein.<br />

Frage 4<br />

Implementieren Sie einen Prozess, der in Abhängigkeit von key die Signale<br />

addr <strong>und</strong> hit treibt.<br />

Hinweise<br />

• Bei Übereinstimmung des Suchschlüssels key mit mehreren CAM-Zeilen<br />

ist stets die höchste Adresse dominant.<br />

• Das Ausgangssignal hit zeigt an, ob der Suchschlüssel key gef<strong>und</strong>en<br />

wurde (hit = ’1’) oder nicht (hit = ’0’).<br />

• In die Suche dürfen nur gültige CAM-Zeilen einbezogen werden.<br />

Für bestimmte Anwendungen, wie beispielsweise bei der hardwaregestützen Dekodierung von<br />

Huffman-Codes, wird eine unscharfe Suche benötigt. Hier<strong>für</strong> kann ein TCAM (Ternary CAM)<br />

genutzt werden, der es ermöglicht, den Vergleich mit den in der Speichermatrix abgelegten<br />

Daten auf einzelne Bits zu beschränken. Der relevante Teil eines Datums wird dabei mit Hilfe<br />

einer Maske mask festgelegt, die zusammen mit dem Datum data in einer CAM-Zeile abgelegt<br />

ist. Gesetzte Bits der Maske zeigen an, dass das Bit an der jeweils entsprechenden Position<br />

beim Vergleich von Suchschlüssel <strong>und</strong> Datum berücksichtigt werden muss. Bild 3 zeigt eine<br />

Zeile eines solchen TCAM.<br />

data mask v<br />

Bild 3<br />

TCAM-Zeile<br />

Aufgabe 2 Seite 8

Dieser TCAM soll nun in Form einer synthetisierbaren Strukturbeschreibung modelliert<br />

werden. Hier<strong>für</strong> wird der TCAM, wie in Bild 4 gezeigt, aus Line-Modulen aufgebaut, die<br />

jeweils eine TCAM-Zeile realisieren. Jede dieser Zeilen besitzt nicht nur den Eingang key <strong>und</strong><br />

die Ausgänge addr_out <strong>und</strong> hit_out, sondern darüber hinaus zwei weitere Eingänge<br />

addr_in <strong>und</strong> hit_in, die es ermöglichen, die Line-Module wie gezeichnet zu kaskadieren.<br />

TCAM<br />

0<br />

key<br />

Line DEPTH–1<br />

hit<br />

addr<br />

Line DEPTH–2<br />

Line 0<br />

addr<br />

hit<br />

Bild 4<br />

TCAM-Struktur<br />

Frage 5<br />

Frage 6<br />

Geben Sie eine synthetisierbare Architecture <strong>für</strong> ein einzelnes Line-Modul an.<br />

Hinweise<br />

• Gehen Sie davon aus, dass die zugehörige Entity neben den generischen<br />

Parametern key_width <strong>und</strong> addr_width einen weiteren generischen<br />

Parameter pos vom Typ natural aufweist, der die Adresse der Zeile im<br />

Speicherarray angibt.<br />

• Die Entity selbst ist nicht verlangt.<br />

• Modellieren Sie den Speicherinhalt einer Zeile mit Hilfe geeigneter<br />

Signale. Diesen Signalen muss in der Architecture kein Wert zugewiesen<br />

werden, da das Schreiben des CAM nicht betrachtet wird.<br />

• Die Priorisierung der Adressen soll wie in Frage 4 erfolgen.<br />

Geben Sie eine vollständige Strukturbeschreibung des TCAM in Form einer<br />

Architecture an. Verwenden Sie dazu Line-Module entsprechend Frage 5.<br />

Aufgabe 2 Seite 9