Musterlösung - Institut für Kommunikationsnetze und ...

Musterlösung - Institut für Kommunikationsnetze und ...

Musterlösung - Institut für Kommunikationsnetze und ...

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

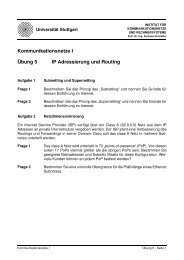

Universität Stuttgart<br />

INSTITUT FÜR<br />

KOMMUNIKATIONSNETZE<br />

UND RECHNERSYSTEME<br />

Prof. Dr.-Ing. Dr. h. c. mult. P. J. Kühn<br />

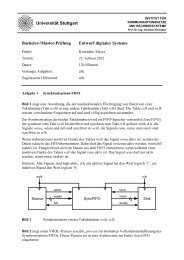

<strong>Musterlösung</strong><br />

Termin:<br />

Entwurf digitaler Systeme<br />

12. Oktober 2007<br />

Aufgabe 1<br />

USB Schnittstelle<br />

Frage 1 a) Wie lange liegt ein einzelnes Bit im Falle der drei Übertragungsraten<br />

9 Punkte jeweils am Sender an?<br />

Low Speed: 667 ns<br />

Full Speed: 83 ns<br />

High Speed: 2.1 ns<br />

b) Wie viele Bits befinden sich bei den drei Übertragungsraten bei einem<br />

Kabel maximaler Länge <strong>und</strong> maximaler Verzögerung jeweils maximal<br />

gleichzeitig auf der Leitung?<br />

Übertragungsdauer 5 m * 5.2 ns/m = 26 ns<br />

Low Speed <strong>und</strong> High Speed: Werte von maximal 2 Bits auf der Leitung<br />

High Speed: Werte von maximal 14 Bits auf der Leitung<br />

c) Welche der drei Übertragungsraten erfordern Vorkehrungen gegen Reflexionen?<br />

Verwenden Sie die Abschätzungsformel aus dem Manuskript.<br />

Gehen Sie näherungsweise von Signalanstiegs- <strong>und</strong> Signalabfallzeiten von<br />

jeweils etwa 20% der Bitdauer aus. Beachten Sie die maximal zulässige<br />

Kabellänge.<br />

v = 1m/5.2ns = 19cm/ns (ca 20 cm/ns)<br />

Low Speed: (t r * v) / 2 = 13.34 m<br />

Full Speed: (t r * v) / 2 = 1.66 m<br />

High Speed: (t r * v) / 2 = 4.2 cm<br />

Fazit: Bei einer Kabellänge von 5 m erfordern der Full Speed Modus <strong>und</strong><br />

der High Speed Modus Vorkehrungen gegen Reflexionen.

Frage 2 a) Wie groß sollte laut Hersteller der Wellenwiderstand der Leiterbahnen <strong>für</strong><br />

8 Punkte die USB-Leitungen D+ <strong>und</strong> D– gegen Masse jeweils sein?<br />

45Ω<br />

b) Warum ist es im Low Speed <strong>und</strong> im Full Speed Modus nicht möglich, die<br />

Leitungen D+ <strong>und</strong> D– am Leitungsende mit einem Pull-up oder Pull-down<br />

Widerstand so abzuschließen, dass Anpassung herrscht?<br />

Die Spannungsdifferenz (voltage swing) in diesen Modi beträgt mindestens<br />

2.5 Volt. Da es sich um bidirektionale Leitungen handelt, muss jede Leitung<br />

an beiden Enden abgeschlossen werden. Daraus ergibt sich eine statische<br />

Treiberbelastung von I = U / (Z / 2) = 2.5V / 22.5 Ω = 111 mA. Treiber mit<br />

derartig hoher Leistung lassen sich nicht integrieren <strong>und</strong> verursachen große<br />

Störungen. Außerdem ist die daraus resultierende Leistungsaufnahme <strong>für</strong><br />

typische USB-Geräte viel zu groß.<br />

c) Warum ist es im High Speed Modus möglich?<br />

Wegen der "low voltage swing"-Signalpegel im High Speed Modus beträgt<br />

die statische Belastung <strong>für</strong> die Treiber in diesem Fall nur noch 350 mV /<br />

22.5 Ω = 16 mA.<br />

Frage 3 a) Entnehmen Sie der Tabelle die Funktion der vier Pins im Full Speed Modus<br />

16 Punkte (Hinweis: Dieser Modus schließt dem Low Speed Modus mit ein.)<br />

DP: Eingang <strong>für</strong> D+<br />

DM: Eingang <strong>für</strong> D–<br />

RSDP: Ausgang <strong>für</strong> D+<br />

RSDM: Ausgang <strong>für</strong> D–<br />

b) Spekulieren Sie über die Bedeutung von "RS" in den Signalbezeichnungen<br />

RSDP <strong>und</strong> RSDM.<br />

R S : Series Resistor, Serienwiderstand.<br />

c) Welche Funktion erfüllen die Widerstände R4 <strong>und</strong> R5 in der Beispielbeschaltung<br />

im Full Speed Modus? Erklären Sie, auf welche Weise diese<br />

Widerstände Reflexionen entgegenwirken.<br />

Diese Widerstände sorgen <strong>für</strong> Anpassung beim Sender anstatt, wie sonst<br />

üblich, beim Empfänger. Die Signalwelle wird vom Empfänger wegen der<br />

hohen Eingangsimpedanz zunächst zurück zum Sender reflektiert. Dort<br />

herrscht wegen der Serienschaltung aus niedriger Treiberimpedanz<br />

(wenige Ω) <strong>und</strong> dem Serienwiderstand Anpassung, d.h. die Welle wird<br />

absorbiert.<br />

d) Wie nennt man diese Form des Leitungsabschlusses?<br />

Serienterminierung (series termination, source termination)<br />

Aufgabe 1 Seite 2

e) Warum ist diese Terminierungsform <strong>für</strong> den High Speed Modus nicht geeignet?<br />

Der Serienwiderstand bildet zusammen mit dem Kapazitätsbelag der Leitung<br />

ein RC-Glied, das als Tiefpass wirkt. Dieser Tiefpass dämpft die <strong>für</strong><br />

den High Speed Modus erforderlichen hohen Frequenzen zu stark.<br />

Frage 4 a) Entnehmen Sie der Tabelle die Funktion der Pins DP <strong>und</strong> DM im High<br />

11 Punkte Speed Modus.<br />

DP: bidirektionale Leitung <strong>für</strong> D+<br />

DM: bidirektionale Leitung <strong>für</strong> D–<br />

b) Welche Funktion erfüllen die Widerstände R4 <strong>und</strong> R5 in der Beispielbeschaltung<br />

nun?<br />

Sie wirken als parallele Abschlusswiderstände.<br />

c) Wie muss der Baustein die Pins RSDP <strong>und</strong> RSDM im High Speed Modus<br />

schalten?<br />

Auf ein konstantes Potential mit geringem Innenwiderstand (wenige Ω).<br />

d) Wie nennt man diese Form des Leitungsabschlusses?<br />

Parallele Terminierung<br />

Frage 5 a) Warum sollen die Leiterbahnen <strong>für</strong> D+ <strong>und</strong> D– möglichst die gleiche Länge<br />

9 Punkte aufweisen?<br />

Damit die Signale beim Empfänger nicht versetzt ankommen.<br />

b) Warum soll die Anzahl von Durchkontaktierungen (vias) <strong>und</strong> Kurven (curves)<br />

so klein wie möglich gehalten werden?<br />

Durchkontaktierungen <strong>und</strong> Kurven führen zu Inhomogenitäten im Wellenwiderstand,<br />

die wiederum zu Reflexionen führen.<br />

c) Warum sollen die in der Beispielbeschaltung fett gezeichneten Leitungen so<br />

kurz wie möglich gehalten werden? Warum ist die Leiterbahnlänge der<br />

nicht fett gezeichneten Leitungsteile nicht so entscheidend?<br />

Die fett gezeichneten Teile realisieren den Leitungsabschluss. Es soll verhindert<br />

werden, dass die Leiterbahnen zwischen Abschlusswiderstand <strong>und</strong><br />

dem Chip auch als Leitungen im leitungstheoretischen Sinne betrachtet<br />

werden müssen.<br />

Die nicht fett gezeichneten Leitungsteile gehören bereits zur eigentlichen<br />

Leitung. Sofern der Wellenwiderstand der Leiterbahnen korrekt ist <strong>und</strong> die<br />

Kombination aus USB-Buchse <strong>und</strong> Stecker keine wesentliche Inhomogenität<br />

verursacht, kommt es auf diesem Leitungsstück zu keinen zusätzlichen<br />

Reflexionen.<br />

d) Warum darf die Versorgungslage unter den Leiterbahnen <strong>für</strong> D+ <strong>und</strong> D–<br />

keine Lücke (power plane void) aufweisen?<br />

Weil sich der Wellenwiderstand des Leitungsstückes über der Lücke ändert.<br />

Aufgabe 1 Seite 3

Aufgabe 2<br />

VHDL-Entwurf<br />

Frage 1<br />

2 Punkte<br />

Frage 2<br />

6 Punkte<br />

Frage 3<br />

3 Punkte<br />

Teil 1<br />

Frage 4<br />

2 Punkte<br />

Geben Sie <strong>für</strong> das in Bild 1 gezeichneten Beispiel den Wert des Feldes mit den<br />

Koordinaten (X = 9, Y = 3) an.<br />

(true, destroyer, vertical, 2, false)<br />

Geben Sie den vollständigen Package Body des Packages types2 an.<br />

package body types2 is<br />

pure function ship_class_to_length(ship_class :<br />

ship_class_type)<br />

return positive is<br />

type lut_type is array(ship_class_type) of positive;<br />

constant lut : lut_type :=<br />

(carrier=>4, destroyer=>3, cruiser=>2, submarine=>1);<br />

begin<br />

return lut(ship_class);<br />

end function ship_class_to_length;<br />

end package body types2;<br />

Aus welchem Gr<strong>und</strong> wurden die Deklarationen in zwei Packages untergliedert<br />

<strong>und</strong> nicht in einem einzigen Package zusammengefasst?<br />

Aus Modularisierungsgründen:<br />

• Das Package types1 enthält ausschließlich die Deklarationen, die zur<br />

Beschreibung der Schnittstellen des aktiven <strong>und</strong> passiven Spielers benötigt<br />

werden.<br />

• Das Package types2 enthält demgegenüber die Deklarationen, die von der<br />

Implementierung des passiven Spielers benötigt werden.<br />

Abstraktes Verhaltensmodell<br />

Geben Sie die Entity passive_player als VHDL-Beschreibung an.<br />

use work.types1.all;<br />

entity passive_player<br />

port(<br />

target : in coord_type;<br />

result : out result_type<br />

);<br />

end entity passive_player;<br />

Aufgabe 2 Seite 4

Frage 5<br />

5 Punkte<br />

Simulieren Sie die oben angegebene Funktion fire mit dem Parameter<br />

target = (2, 4) "von Hand". Gehen Sie davon aus, dass die Variable board<br />

entsprechend Bild 1 initialisiert wurde.<br />

Geben Sie dazu in einer Tabelle die Werte der Variablen ship_length,<br />

first_field_coord, current_field, number_of_hits, i <strong>und</strong><br />

result vor Eintritt in die entsprechende Schleife, am Ende jedes Schleifendurchlaufs<br />

sowie unmittelbar vor dem Funktionsende an.<br />

Vor Eintritt in<br />

Schleife<br />

Ende Schleifendurchlauf<br />

i = 0<br />

Ende Schleifendurchlauf<br />

i = 1<br />

Ende Schleifendurchlauf<br />

i = 2<br />

Ende Schleifendurchlauf<br />

i = 3<br />

Vor Funktionsende<br />

ship<br />

length<br />

first<br />

field<br />

coord<br />

current field<br />

number<br />

of<br />

hits<br />

4 (1,4) (true, carrier, horizontal, 1, false) 0 - hit<br />

4 (1,4) (true, carrier, horizontal, 1, false) 0 0 hit<br />

4 (1,4) (true, carrier, horizontal, 1, false) 1 1 hit<br />

4 (1,4) (true, carrier, horizontal, 1, false) 1 2 hit<br />

4 (1,4) (true, carrier, horizontal, 1, false) 1 3 hit<br />

4 (1,4) (true, carrier, horizontal, 1, false) 1 - hit<br />

i<br />

result<br />

Frage 6<br />

6 Punkte<br />

Die gegebene Verhaltensbeschreibung ist nicht synthetisierbar. Warum? Geben<br />

Sie mögliche Gründe da<strong>für</strong> an.<br />

Gr<strong>und</strong>sätzlich gilt: Beschreibungen, denen ein Modell auf der Register-Transfer-<br />

Ebene zugr<strong>und</strong>e liegt, sind mit hoher Wahrscheinlichkeit synthetisierbar.<br />

Mögliche Probleme der gegeben Beschreibung:<br />

• wait-Anweisung:<br />

• wait-Anweisungen an beliebiger Stelle (nicht am Anfang/Ende eines<br />

Prozesses)<br />

• Warten auf einen Vorgangs (transaction) statt auf ein Ereignis (event)<br />

• Fehlen eines Taktsignals<br />

• board <strong>und</strong> live_ships_count müssen als Speicher/Register realisiert<br />

werden. Wie genau dies zu geschehen hat, ist unklar. Beispielsweise muss<br />

in einem Simulationszyklus auf bis zu vier Elemente der Variable board<br />

zugegriffen werden.<br />

• Schleifen müssen <strong>für</strong> die Synthese "abgerollt" werden. Dies ist im vorliegenden<br />

Fall schwierig, da die Anzahl der Schleifendurchläufe nicht im voraus<br />

bekannt ist.<br />

Aufgabe 2 Seite 5

Frage 7<br />

4 Punkte<br />

Teil 2<br />

Frage 8<br />

4 Punkte<br />

Könnte die Anweisung wait on target’transaction in der Endlosschleife<br />

des Prozesses main durch die Anweisung wait on target ersetzt<br />

werden? Beziehen Sie Ihre Antwort auf den vorliegenden Fall!<br />

Durch das Warten auf eine Transaction wird die Funktion fire auch dann ausgeführt,<br />

wenn nacheinander mehrere Male auf dasselbe Feld gefeuert wird. Wird<br />

ein Schiff versenkt, liefert die Funktion beim ersten Aufruf sunk, bei folgenden<br />

Aufrufen mit den gleichen Koordinaten nur noch hit.<br />

Wartet man stattdessen auf ein Event, so wird die Funktion fire nur ein Mal<br />

ausgeführt, wenn nacheinander mehrere Male auf dasselbe Feld gefeuert wird.<br />

Das bedeutet, dass das Signal result bei wiederholten Schüssen auf dasselbe<br />

Feld seinen ursprünglichen Wert behält <strong>und</strong> darüber hinaus auch keine Transaction<br />

aufweist.<br />

Schließt man den Fall aus, dass mehrere Male auf dasselbe Feld gefeuert werden<br />

kann, so verhalten sich die beiden unterschiedlichen Wait-Anweisungen identisch.<br />

Synthetisierbares RTL-Modell<br />

Aus welchen Gründen muss die Schnittstelle des synthetisierbaren Modells von<br />

der des abstrakten Modells aus Teil 1 abweichen?<br />

• Als synchrones System muss die Realisierung mit einem Takt- <strong>und</strong> Reset-<br />

Signal versorgt werden.<br />

• Damit aktiver <strong>und</strong> passiver Spieler Daten austauschen können, muss ein<br />

Protokoll definiert werden, dass anzeigt, wann die ausgetauschten Daten<br />

gültig sind. Hier<strong>für</strong> sind zusätzliche Steuerleitungen nötig.<br />

Anmerkung: In der Realisierung aus Teil 1 wurde dem Gegenspieler das<br />

Anliegen neuer Daten implizit durch das Auftreten von Transactions (Vorgängen)<br />

auf den Datensignalen angezeigt.<br />

Aufgabe 2 Seite 6

Frage 9<br />

12 Punkte<br />

a) Zeichnen Sie ein Blockschaltbild auf Register-Transfer-Ebene, das in seiner<br />

Funktion mit obiger Architecture übereinstimmt. Verwenden Sie ausschließlich<br />

Elemente der Register-Transfer-Ebene wie beispielsweise Register,<br />

Multiplexer, Addierer <strong>und</strong> ggf. einzelne Gatter.<br />

sub_value<br />

load_value<br />

command1<br />

command0<br />

#1<br />

+ + + -<br />

01<br />

10 11<br />

>=1<br />

ena<br />

coord<br />

b) Warum sind die internen Verbindungsleitungen in Ihrem Blockschaltbild in<br />

der Architecture behav als Variablen <strong>und</strong> nicht als Signale realisiert?<br />

Allgemein gilt:<br />

• Variablen halten Zwischenergebnisse innerhalb eines einzelnen Prozesses.<br />

• Signale dienen der Kommunikation zwischen Prozessen.<br />

In der Architecture behav sind sämtliche Verbindungsleitungen Teil eines<br />

einzigen Prozesses <strong>und</strong> werden deshalb als Variablen realisiert.<br />

Aufgabe 2 Seite 7

c) In welcher Form müsste man die Architecture prinzipiell beschreiben, damit<br />

diese Verbindungsleitungen in VHDL tatsächlich als Signale modelliert<br />

werden?<br />

Die im Blockschaltbild verwendeten Elemente der Register-Transfer-Ebene<br />

(Addierer, Multiplexer, Register, Oder-Gatter) müssten jeweils als seperate<br />

Prozesse (oder Components) modelliert werden.<br />

Frage 10 a) Wie viele Einträge muss der Speicher aufweisen, wenn die Einheit<br />

8 Punkte generate_address das Signal selected_address auf folgende<br />

Weise erzeugt?<br />

selected_address

c) Geben Sie einen Prozess zur Ermittlung des Folgezustands des Automaten<br />

an.<br />

process(current_state, target_valid, rdata.is_ship,<br />

rdata.ship_class, hit_count, ship_count_is_zero) is<br />

begin<br />

case current_state is<br />

when IDLE =><br />

if target_valid = ’1’ then<br />

next_state <br />

if rdata.is_ship = false then<br />

next_state next_state next_state next_state next_state <br />

next_state <br />

next_state <br />

next_state <br />

next_state <br />

if class_to_length(rdata.ship_class) =<br />

to_integer(hit_count) then<br />

next_state

d) Geben Sie einen separaten Prozess zur Erzeugung der Ausgangssignale an.<br />

process(current_state) is<br />

begin<br />

result_valid