Prüfung - Institut für Kommunikationsnetze und Rechnersysteme ...

Prüfung - Institut für Kommunikationsnetze und Rechnersysteme ...

Prüfung - Institut für Kommunikationsnetze und Rechnersysteme ...

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Universität Stuttgart<br />

INSTITUT FÜR<br />

KOMMUNIKATIONSNETZE<br />

UND RECHNERSYSTEME<br />

Prof. Dr.-Ing. Andreas Kirstädter<br />

Bachelor-<strong>Prüfung</strong><br />

Prüfer:<br />

Termin:<br />

Dauer:<br />

Verlangte Aufgaben:<br />

Zugelassene Hilfsmittel:<br />

Technische Informatik I<br />

Kirstädter, Meyer<br />

19. März 2012<br />

120 Minuten<br />

alle<br />

alle<br />

Aufgabe 1<br />

Assemblerprogrammierung <strong>und</strong> Mikroprogrammierung<br />

Der aus der Vorlesung bekannte Minimalprozessor wird um eine Registereinheit mit zwei Registern<br />

R0 <strong>und</strong> R1 erweitert. Eine neue Adressierungsart Register direkt, kurz Rp (p = 0, 1),<br />

ermöglicht den Zugriff auf diese Register <strong>und</strong> kann mit allen Befehlen verwendet werden, die<br />

auch die Speicher-direkte Adressierung (m) bzw. die Speicher-indirekte Adressierung ((m))<br />

unterstützen, d.h. Rp <strong>und</strong> STORE Rp.<br />

Beispiele: ADD R0 addiere R0 zum Akkumulatorregister AC<br />

LOAD R1 kopiere R1 in das Akkumulatorregister AC<br />

STORE R1 kopiere den Wert des Akkumulatorregisters AC nach R1<br />

Frage 1<br />

Warum beschleunigt die Verwendung der neuen Adressierungsart die Ausführung<br />

von Programmen auch dann, wenn man davon ausgeht, dass der Minimalprozessor<br />

Speicherzugriffe innerhalb eines Taktes abschließt?<br />

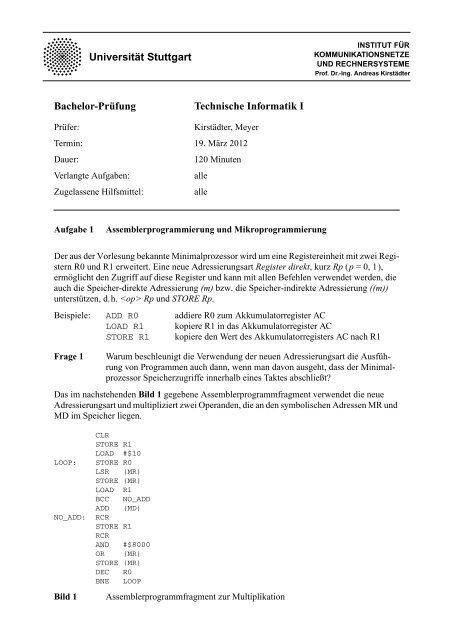

Das im nachstehenden Bild 1 gegebene Assemblerprogrammfragment verwendet die neue<br />

Adressierungsart <strong>und</strong> multipliziert zwei Operanden, die an den symbolischen Adressen MR <strong>und</strong><br />

MD im Speicher liegen.<br />

CLR<br />

STORE R1<br />

LOAD #$10<br />

LOOP: STORE R0<br />

LSR (MR)<br />

STORE (MR)<br />

LOAD R1<br />

BCC NO_ADD<br />

ADD (MD)<br />

NO_ADD: RCR<br />

STORE R1<br />

RCR<br />

AND #$8000<br />

OR (MR)<br />

STORE (MR)<br />

DEC R0<br />

BNE LOOP<br />

Bild 1<br />

Assemblerprogrammfragment zur Multiplikation

Der Original-Minimalprozessor verwendet Bit 8 <strong>und</strong> Bit 9 in einem Befehlswort zur Codierung<br />

der Adressierungsarten implizit, unmittelbar, direkt <strong>und</strong> indirekt. Zur Codierung der neuen<br />

Adressierungsart wird ein weiteres Bit (Bit 10) benötigt, <strong>und</strong> es gelte die in der nachstehenden<br />

Tabelle angegebene Codierung.<br />

Bit 10 Bit 9 Bit 8 Adressierungsart<br />

0 0 0 implizit<br />

0 0 1 #i unmittelbar<br />

0 1 0 (m) Speicher direkt<br />

0 1 1 ((m)) Speicher indirekt<br />

1 0 0 R0 Register R0 direkt<br />

1 0 1 R1 Register R1 direkt<br />

1 1 0 reserviert<br />

1 1 1 reserviert<br />

Bild 2<br />

Frage 2<br />

Codierung der neuen Adressierungsart Register direkt<br />

Geben Sie den Maschinencode <strong>für</strong> das Programm vollständig in hexadezimaler<br />

Schreibweise an. Gehen Sie dabei davon aus, dass MR = $FF61 <strong>und</strong><br />

MD = $FF62.<br />

Frage 3 a) Vor der Ausführung des in Bild 1 gegebenen Programmfragments befinde<br />

sich im Speicherwort an der Adresse MR der Wert $0202, entsprechend im<br />

Speicherwort an der Adresse MD der Wert $0083.<br />

Geben Sie am Ende jedes Schleifendurchlaufs den Wert der Register R0, R1<br />

<strong>und</strong> den Wert des Speicherworts an der symbolischen Adresse MR in Form<br />

einer Tabelle an.<br />

Hinweis: Die Befehle LOAD <strong>und</strong> STORE des Minimalprozessors<br />

verändern die Flags im Statusregister nicht.<br />

b) Liefert der Algorithmus ein 16 Bit breites Ergebnis oder ein 32 Bit breites<br />

Ergebnis? Begründen Sie Ihre Antwort!<br />

c) Realisiert der durch das Programmfragment implementierte Algorithmus<br />

eine vorzeichenbehaftete oder eine vorzeichenlose Multiplikation?<br />

Begründen Sie Ihre Antwort!<br />

Frage 4 a) Optimieren Sie das Programmfragment in Bild 1 hinsichtlich Speicherplatzbedarf<br />

<strong>und</strong> Ausführungszeit, indem Sie die Operationen auf MR<br />

effizienter realisieren. Die Registerbelegung soll dabei zunächst noch<br />

unverändert bleiben.<br />

Hinweis: Die Lösung enthält drei Befehle weniger <strong>und</strong> nur noch 3 Operationen<br />

auf MR.<br />

b) Lässt sich das Programmfragment durch eine effizientere Verwendung der<br />

Register weiter optimieren? Begründen Sie Ihre Antwort!<br />

Aufgabe 1 Seite 2

Nun soll die Hardware des Minimalprozessors um die Registereinheit ergänzt <strong>und</strong> die Mikroprogramme<br />

zur Unterstützung der neuen Adressierungsart entwickelt werden. Die Hardware-<br />

Struktur der Registereinheit zeigt Bild 3.<br />

IX<br />

R0<br />

R1<br />

ED<br />

Bild 3<br />

Registereinheit<br />

Eine neue Mikrooperation f(Rp,AC) → AC abstrahiere das Lesen der Register R0 <strong>und</strong> R1 (in<br />

Ergänzung zur bestehenden Mikrooperation f(MX,AC) → AC). Entsprechend abstrahiert eine<br />

neue Mikrooperation AC → Rp das Schreiben der Register R0 <strong>und</strong> R1.<br />

Frage 5 a) Wie kann auf einfache Weise die Steuerleitung <strong>für</strong> den in Bild 3 dargestellten<br />

Multiplexer erzeugt werden?<br />

b) Worauf muss dann bei der Mikroprogrammierung geachtet werden?<br />

Frage 6<br />

Frage 7<br />

Wie muss die bestehende Speicherregistereinheit des Minimalprozessors ergänzt<br />

werden, damit die neue Registereinheit in den Prozessor integriert werden kann?<br />

Wie viele zusätzliche Steuerleitungen muss das Steuerwerk <strong>für</strong> die Erweiterung<br />

um die Registereinheit erzeugen? Definieren Sie die Funktion dieser Steuerleitungen<br />

<strong>und</strong> bezeichnen Sie diese sinnvoll!<br />

Frage 8 a) Geben Sie ein möglichst effizientes Mikroprogramm zur Implementierung<br />

des Befehls Rp an. Abstrakte Mikroassemblersyntax genügt, die<br />

Codierung auf Steuerleitungsebene ist nicht verlangt.<br />

b) Geben Sie ein möglichst effizientes Mikroprogramm zur Implementierung<br />

des Befehls STORE Rp an. Abstrakte Mikroassemblersyntax genügt, die<br />

Codierung auf Steuerleitungsebene ist nicht verlangt.<br />

c) Vergleichen Sie die Ausführungsdauer der Befehle aus Frage 8a) <strong>und</strong> b) mit<br />

der neuen Adressierungsart Register direkt mit der Ausführungsdauer dieser<br />

Befehle mit den bestehenden Adressierungsarten implizit, unmittelbar,<br />

Speicher-direkt <strong>und</strong> Speicher-indirekt.<br />

Aufgabe 1 Seite 3

Abschließend soll zusätzlich die Adressierungsart Register indirekt implementiert werden.<br />

Dazu werde die Tabelle in Bild 2 wie im nachfolgenden Bild 4 ergänzt.<br />

Bit 10 Bit 9 Bit 8 Adressierungsart<br />

1 1 0 (R0) R0 indirekt<br />

1 1 1 (R1) R1 indirekt<br />

Bild 4<br />

Codierung der neuen Adressierungsart Register indirekt<br />

Für die Realisierung der neuen Adressierungsarten sollen zwei neue Mikrooperationen<br />

Rp → AC <strong>und</strong> MX → AC implementiert werden, die unabhängig von den Bits 0 bis 7 des<br />

Befehlswortes den Inhalt von Rp bzw. MX in das Akkumulatorregister kopieren.<br />

Frage 9<br />

Beschreiben Sie stichwortartig, welche Erweiterungen der Hardware erforderlich<br />

sind, um diese Mikrooperationen zu implementieren.<br />

Verwenden Sie zur Beantwortung von Frage 10 die Hardware-Erweiterungen aus Frage 9.<br />

Weitere Hardware-Erweiterungen sind zunächst nicht zulässig.<br />

Frage 10 a) Geben Sie ein möglichst effizientes Mikroprogramm zur Implementierung<br />

des Befehls (Rp) an. Abstrakte Mikroassemblersyntax genügt, die<br />

Codierung auf Steuerleitungsebene ist nicht verlangt.<br />

b) Geben Sie ein möglichst effizientes Mikroprogramm zur Implementierung<br />

des Befehls STORE (Rp) an. Abstrakte Mikroassemblersyntax genügt, die<br />

Codierung auf Steuerleitungsebene ist nicht verlangt.<br />

Frage 11 a) Skizzieren Sie, durch welche Hardware-Erweiterungen Befehle mit der<br />

Adressierungsart Register indirekt optimiert werden könnten. Definieren<br />

Sie dazu erforderliche Steuerleitungen <strong>und</strong> geben Sie deren Funktion an.<br />

b) Wie viele Takte lassen sich durch Ihre Erweiterungen in den beiden Mikroprogrammen<br />

nach Frage 10 jeweils einsparen?<br />

Aufgabe 1 Seite 4

Aufgabe 2<br />

Virtueller Speicher<br />

Zur Untersuchung der Mechanismen in einer modernen Speicherhierarchie werde beispielhaft<br />

ein Rechnersystem mit unrealistisch kleinen Kenngrößen betrachtet:<br />

• Datenwortbreite: 1 Byte<br />

• Größe eines virtuellen Adressraums: 64 kByte, d.h. virtuelle Adressen mit 16 Bit<br />

• Größe des physikalischen Adressraums: 64 kByte, d.h. physikalische Adressen mit 16 Bit<br />

• Seitengröße: 4 kByte<br />

• Maximal mögliche Anzahl virtueller Adressräume: 16<br />

Betrachtet werde die Abbildung dreier virtueller Adressräume A, B <strong>und</strong> C auf einen physikalischen<br />

Adressraum. Bild 1 zeigt die von einem Betriebssystem vorgegebenen Übersetzungsvorschriften<br />

zu einem betrachteten Zeitpunkt.<br />

virtueller Adressraum A virtueller Adressraum B virtueller Adressraum C<br />

Seitennr. Rahmennr. Seitennr. Rahmennr. Seitennr. Rahmennr.<br />

0 2 0 5 0 1<br />

1 3 1 – 1 –<br />

2 – 2 – 2 –<br />

3 – 3 – 3 –<br />

4 – 4 – 4 –<br />

5 – 5 – 5 –<br />

6 – 6 – 6 –<br />

7 – 7 14 7 –<br />

8 12 8 15 8 –<br />

9 13 9 10 9 8<br />

10 6 10 0 10 9<br />

11 – 11 – 11 –<br />

12 – 12 – 12 –<br />

13 – 13 – 13 –<br />

14 – 14 – 14 –<br />

15 4 15 – 15 11<br />

Bild 1<br />

Adressübersetzungstabellen <strong>für</strong> drei virtuelle Adressräume A, B <strong>und</strong> C<br />

Frage 1 a) Aus welchen Gründen nutzen viele <strong>Rechnersysteme</strong> das Konzept des virtuellen<br />

Speichers?<br />

b) Wo treten in einem Rechnersystem virtuelle Adressen, wo physikalische<br />

Adressen auf?<br />

c) Warum wird die Adressübersetzung in realen Systemen nicht mit einstufigen<br />

Tabellen wie in Bild 1 realisiert?<br />

Aufgabe 2 Seite 5

Frage 2 a) Wie viele Bit umfasst eine virtuelle Seitennummer im vorliegenden<br />

"Einfach"-Beispiel?<br />

b) Skizzieren Sie einen unvollständigen zweistufigen Baum, der der einstufigen<br />

Übersetzungstabelle <strong>für</strong> den virtuellen Adressraum A (Bild 1)<br />

entspricht. Teilen Sie die zu übersetzenden Bits der virtuellen Seitennummer<br />

gleichmäßig auf die beiden Ebenen auf.<br />

c) Vergleichen Sie <strong>für</strong> den betrachteten Fall (virtueller Adressraum A) den<br />

Speicherbedarf <strong>für</strong> die einstufige Tabelle mit dem Speicherbedarf <strong>für</strong> den<br />

unvollständigen zweistufigen Baum. Erklären Sie das Ergebnis!<br />

Gehen Sie bei Ihren Überlegungen davon aus, dass <strong>für</strong> jeden Eintrag der<br />

Seitentabelle unabhängig von der Ebene jeweils ein Speicherwort (d.h. im<br />

vorliegenden Fall ein Byte) verwendet wird.<br />

Nachfolgend werde die Adressübersetzung mit Hilfe einer invertierten Seitentabelle betrachtet.<br />

Frage 3 a) Welche potenziellen Vorteile bietet eine invertierte Seitentabelle im<br />

Vergleich mit einer nicht-invertierten Seitentabelle?<br />

b) Welches Problem muss man bei der invertierten Seitentabelle im Gegenzug<br />

lösen?<br />

c) Geben Sie nur <strong>für</strong> den virtuellen Adressraum A (Bild 1) eine einfache<br />

invertierte Seitentabelle an. Ein Eintrag der Tabelle soll nur die entsprechende<br />

virtuelle Seitennummer enthalten, d.h. insbesondere noch kein<br />

Link-Feld. Weiterhin ist hier nur die invertierte Seitentabelle selbst<br />

verlangt, d.h. ohne Hash-Generator <strong>und</strong> ohne Hash-Anker-Tabelle.<br />

Eine invertierte Seitentabelle ist in der Lage, einen virtuellen Adressraum auf den physikalischen<br />

Adressraum abzubilden. Um mehrere virtuelle Adressräume zu unterstützen, ergänzt man<br />

virtuelle Adressen um einen sogenannten Virtual Address Space Identifier, der den zugehörigen<br />

virtuellen Adressraum eindeutig kennzeichnet. Das entstehende Paar aus Virtual Address<br />

Space Identifier <strong>und</strong> virtueller Adresse wird nachfolgend als globale virtuelle Adresse<br />

bezeichnet, entsprechend wird eine virtuelle Adresse innerhalb eines virtuellen Adressraums als<br />

lokale virtuelle Adresse bezeichnet.<br />

Angewandt auf das betrachtete Einfachbeispiel mit maximal 16 virtuellen Adressräumen<br />

bedeutet dies, dass jede 16 Bit breite lokale virtuelle Adresse um einen 4 Bit breiten Virtual<br />

Address Space Identifier erweitert wird. Dadurch entstehen globale virtuelle Adressen mit 20<br />

Bit <strong>und</strong> ein globaler virtueller Adressraum mit 1 MByte. Entsprechend besteht die Aufgabe der<br />

Adressübersetzung darin, 8 Bit breite globale virtuelle Seitennummern auf 4 Bit breite physikalische<br />

Rahmennummern abzubilden.<br />

Für die Virtual Address Space Identifier im Beispiel gelte "1010" <strong>für</strong> Adressraum A, "1011" <strong>für</strong><br />

Adressraum B <strong>und</strong> "1100" <strong>für</strong> Adressraum C.<br />

Frage 4 Geben Sie eine invertierte Seitentabelle <strong>für</strong> die Übersetzung aller drei in Bild 1<br />

enthaltenen virtuellen Adressräume an. Ein Eintrag der Tabelle soll zunächst nur<br />

die entsprechende globale virtuelle Seitennummer enthalten (vorzugsweise als<br />

zweistellige Hexadezimalzahl), bestehend aus Virtual Address Space Identifier<br />

<strong>und</strong> lokaler Seitennummer, d.h. insbesondere noch kein Link-Feld. Weiterhin ist<br />

nur die invertierte Seitentabelle selbst verlangt, d.h. ohne Hash-Generator <strong>und</strong><br />

ohne Hash-Anker-Tabelle.<br />

Aufgabe 2 Seite 6

Um eine globale virtuelle Seitennummer in die zugehörige physikalische Rahmennummer zu<br />

übersetzen, muss die globale virtuelle Seitennummer in der invertierten Seitentabelle gesucht<br />

werden. Zur Beschleunigung dieser Suche verwendet man einen Hash-Generator <strong>und</strong> eine<br />

Hash-Anker-Tabelle.<br />

Nachfolgend soll der Hash-Generator die einfache Hash-Funktion "modulo 2 4 " verwenden, d.h.<br />

der Hash-Wert einer globalen virtuellen Seitennummer ist die zugehörige lokale virtuelle Seitennummer.<br />

Frage 5 a) Beginnen Sie die Konstruktion der Hash-Anker-Tabelle. Berücksichtigen<br />

Sie zuerst nur den virtuellen Adressraum A.<br />

Zur Hilfe sei der erste Eintrag der Hash-Anker-Tabelle als Beispiel<br />

gegeben: Die globale Seitennummer $A0 (Adressraum A, Seite 0) soll laut<br />

Bild 1 auf die physikalische Rahmennummer 2 abgebildet werden. Der<br />

Hash-Wert der globalen virtuellen Seitennummer $A0 ist 0, d.h. die Hash-<br />

Anker-Tabelle muss am Index 0 den Wert 2 enthalten.<br />

b) Treten dabei Hash-Kollisionen auf? Begründen Sie Ihre Antwort!<br />

c) Ergänzen Sie die Hash-Anker-Tabelle nun um die Einträge zur Übersetzung<br />

des virtuellen Adressraums B.<br />

d) Lösen Sie die dabei auftretenden Hash-Kollisionen auf, indem Sie jedem<br />

Eintrag der invertierten Seitentabelle ein Link-Feld hinzufügen. Geben Sie<br />

den Inhalt der relevanten Link-Felder an!<br />

e) Ergänzen Sie die Hash-Anker-Tabelle <strong>und</strong> die Link-Felder analog zu c) <strong>und</strong><br />

d) um die Einträge zur Übersetzung des virtuellen Adressraums C.<br />

f) Wie viele Speicherzugriffe sind mit Hilfe dieser invertierten Seitentabelle<br />

zur Adressübersetzung im Mittel erforderlich? Gehen Sie von folgenden<br />

Voraussetzungen aus:<br />

• Es werden nur Zugriffe auf Seiten betrachtet, denen nach Bild 1 ein<br />

physikalischer Rahmen zugeordnet ist.<br />

• Zugriffe auf diese Seiten treten gleichwahrscheinlich auf.<br />

• Ein Zugriff auf die Hash-Anker-Tabelle kostet einen Speicherzugriff.<br />

• Ein Zugriff auf das Feld "globale virtuelle Seitennummer" in der invertierten<br />

Seitentabelle kostet einen Speicherzugriff.<br />

• Ein Zugriff auf das Link-Feld der invertierten Seitentabelle kostet<br />

einen Speicherzugriff.<br />

Aufgabe 2 Seite 7

Um die Anzahl an Kollisionen zu verringern, soll die Kapazität der Hash-Anker-Tabelle verdoppelt<br />

werden, d.h. sie weise jetzt 32 Einträge auf. Entsprechend verwende der Hash-Generator<br />

die Hash-Funktion "modulo 2 5 ".<br />

Frage 6 a) Geben Sie die komplette Hash-Anker-Tabelle <strong>und</strong> den Wert aller Link-<br />

Felder der invertierten Seitentabelle an. Gehen Sie wieder davon aus, dass<br />

zuerst die Zuordnungen <strong>für</strong> den virtuellen Adressraum A eingetragen<br />

werden, dann die Einträge <strong>für</strong> den virtuellen Adressraum B <strong>und</strong> schließlich<br />

die <strong>für</strong> den virtuellen Adressraum C.<br />

b) Wie viele Speicherzugriffe sind jetzt zur Adressübersetzung im Mittel<br />

erforderlich? Gehen Sie von denselben Voraussetzungen wie bei Frage 5f)<br />

aus.<br />

Frage 7 a) Konstruieren Sie eine Hash-Funktion, die bei Verwendung einer Hash-<br />

Anker-Tabelle mit wieder nur 16 Einträgen im Fall des betrachteten<br />

Beispiels (Bild 1) eine bessere Leistung aufweist als die ursprüngliche<br />

Hash-Funktion "modulo 2 4 ".<br />

b) Weisen Sie die bessere Leistung Ihrer Hash-Funktion analog zu Frage 5f)<br />

bzw. Frage 6b) nach!<br />

Zur weiteren Beschleunigung der Adressübersetzung soll ein Address Translation Cache (ATC)<br />

verwendet werden. Der ATC setze lokale virtuelle Seitennummern auf physikalische Rahmennummern<br />

um. Er sei vollassoziativ <strong>und</strong> weise vier Einträge auf.<br />

Frage 8 a) Wie viele Bits werden im vorliegenden Einfachbeispiel pro Eintrag <strong>für</strong> den<br />

Tag benötigt?<br />

b) Benötigt ein ATC sogenannte "Dirty"-Bits? Begründen Sie Ihre Antwort!<br />

c) Erklären Sie stichwortartig, wie man die Ersetzungsstrategie "Least<br />

Recently Used" im vorliegenden Fall exakt in Software lösen könnte.<br />

Wäre eine solche Lösung praktikabel?<br />

d) Wie groß darf ein vierfach mengenassoziativer Cache im vorliegenden Fall<br />

maximal sein, damit der Zugriff auf den Cache <strong>und</strong> die Adressübersetzung<br />

mit Hilfe des ATC parallel möglich sind?<br />

Frage 9 a) Welchen großen Vorteil hätte es allgemein, wenn ein ATC statt lokalen<br />

virtuellen Adressen (bzw. Seitennummern) eindeutige globale virtuelle<br />

Adressen verarbeiten würde?<br />

b) Spekulieren Sie, warum man trotz dieses Vorteils in der Praxis einen ATC<br />

nur mit lokalen virtuellen Adressen betreibt.<br />

Aufgabe 2 Seite 8