Musterlösung - Institut für Kommunikationsnetze und ...

Musterlösung - Institut für Kommunikationsnetze und ...

Musterlösung - Institut für Kommunikationsnetze und ...

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

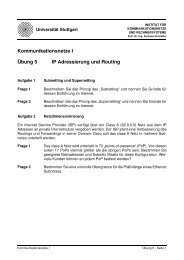

Universität Stuttgart<br />

INSTITUT FÜR<br />

KOMMUNIKATIONSNETZE<br />

UND RECHNERSYSTEME<br />

Prof. Dr.-Ing. Andreas Kirstädter<br />

<strong>Musterlösung</strong><br />

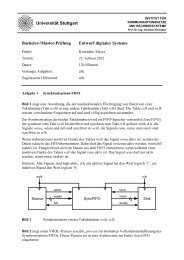

Entwurf digitaler Systeme<br />

Termin:<br />

4. März 2010<br />

Aufgabe 1<br />

Verhaltensbeschreibung eines Multiplizierwerks<br />

Frage 1 a) Wie oft wird die im Prozess enthaltene Schleife ausgeführt?<br />

(6 Punkte)<br />

5 Mal<br />

b) Wie viele Elemente weist das Array ac auf?<br />

10 Elemente<br />

c) Welchen Typ haben die Elemente des Arrays ac?<br />

std_logic<br />

Frage 2<br />

(10 Punkte)<br />

Frage 3<br />

(4 Punkte)<br />

Geben Sie den Wert der Variablen ac am Ende jedes Schleifendurchlaufs an.<br />

0000000000<br />

0000010101<br />

0000101010<br />

0001010100<br />

0010111101 (189 = 21 * 9)<br />

Wie viele Delta-Zyklen nach den Events auf den Eingangsports a <strong>und</strong> b nimmt<br />

der Ausgangsport p den Wert des Produktes an?<br />

einen Delta-Zyklus später<br />

Frage 4<br />

(8 Punkte)<br />

Welchen Wert nähme der Ausgangsport p im vorliegenden Beispiel an, wenn<br />

man ac in Form eines Signals anstelle einer Variablen modellieren würde?<br />

ac nimmt zum Simulationsstart den Wert UUUUUUUUUU an<br />

Signalzuweisungen (einschließlich der Initialisierung) wirken sich erst aus,<br />

wenn der Prozess suspendiert wird (d.h. hier am Ende des Prozesses). Deshalb<br />

wird als Wert <strong>für</strong> ac im Prozess UUUUUUUUUU gelesen.<br />

Die einzige Ergebnis-Stelle, die unabhängig vom Initialwert von ac ist, ist die<br />

Stelle ac(0). Sie muss wegen ac := ac(ac’LEFT - 1 DOWNTO 0) & ’0’;<br />

auf jeden Fall Null sein.<br />

Deshalb nähme p in diesem Fall den Wert UUUUUUUUU0 an.

Frage 5 a) Wird ein Synthesewerkzeug den Prozess in der Architecture behav als<br />

(23 Punkte) kombinatorisches oder als sequenzielles Netzwerk realisieren? Begründen<br />

Sie Ihre Antwort!<br />

Als kombinatorisches Netzwerk. Die Schleife kann einfach abgerollt werden,<br />

wodurch eine Struktur mit 4 Addieren entsteht.<br />

b) Skizzieren Sie ganz grob die Schaltung auf RT-Ebene, die ein Synthesewerkzeug<br />

aus der Beschreibung erzeugen wird. Gehen Sie dabei davon aus, dass<br />

die Zieltechnologie (z.B. FPGAs) über ausreichend breite Addierer verfügt,<br />

nicht aber über Multiplizierer.<br />

a<br />

5<br />

&&&&&<br />

a<br />

5 5<br />

&&&&&<br />

6 5<br />

b(4)<br />

b(3)<br />

+<br />

7<br />

8<br />

a<br />

5<br />

&&&&&<br />

5<br />

b(2)<br />

+<br />

8<br />

9<br />

a<br />

&&&&&<br />

+ a<br />

9<br />

10<br />

+<br />

5<br />

5<br />

5<br />

&&&&&<br />

5<br />

b(1)<br />

b(0)<br />

p<br />

10<br />

Aufgabe 1 Seite 2

Aufgabe 2<br />

Strukturbeschreibung eines Dividierwerks<br />

Teil 1<br />

Komponenten des Dividierwerks<br />

Frage 1<br />

(18 Punkte)<br />

a) Geben Sie die VHDL-Entity mux2 <strong>für</strong> den in Bild 1 verwendeten Multiplexer<br />

an. Die Wortbreite der beiden Eingangsoperanden <strong>und</strong> des Ausgangsoperanden<br />

soll über einen generischen Parameter N festgelegt werden. Nennen<br />

Sie die Eingangsports x0 <strong>und</strong> x1, den Auswahleingang s <strong>und</strong> den Ausgangsport<br />

z.<br />

LIBRARY ieee; USE ieee.std_logic_1164.ALL;<br />

ENTITY mux2 IS<br />

GENERIC(N: positive);<br />

PORT(<br />

s: IN std_logic;<br />

x0, x1: IN std_logic_vector(N-1 DOWNTO 0);<br />

z: OUT std_logic_vector(N-1 DOWNTO 0));<br />

END ENTITY mux2;<br />

b) Welchen Typ verwenden Sie <strong>für</strong> den generischen Parameter N sinnvollerweise?<br />

Begründen Sie Ihre Antwort!<br />

Den Typ "positive", weil N ganzzahlig <strong>und</strong> mindestens 1 sein muss.<br />

c) Geben Sie eine vollständige VHDL-Architecture behav <strong>für</strong> die Entity mux2<br />

an, die das Verhalten des Multiplexers beschreibt.<br />

ARCHITECTURE behav OF mux2 IS<br />

BEGIN<br />

z

Frage 2<br />

(10 Punkte)<br />

Geben Sie eine vollständige Architecture behav zur Entity au in Form einer<br />

Verhaltensbeschreibung an. Verwenden Sie dazu das Package ieee.numeric_std.<br />

ARCHITECTURE behav OF au IS<br />

BEGIN<br />

process(mode, x, y) is<br />

variable xv, yv: unsigned(N downto 0);<br />

variable zv: unsigned(N downto 0);<br />

begin<br />

xv := unsigned(’0’ & x);<br />

yv := unsigned(’0’ & y);<br />

if mode = ’1’ then<br />

zv := xv - yv;<br />

else<br />

zv := xv + yv;<br />

end if;<br />

z

Frage 4<br />

(10 Punkte)<br />

Vervollständigen Sie die nachfolgende Tabelle:<br />

mode AC MQ<br />

Initialzustand 1 0000 1110<br />

nach 1. Taktflanke 0 1110 1100<br />

nach 2. Taktflanke 1 0001 1100<br />

nach 3. Taktflanke 1 0000 1001<br />

nach 4. Taktflanke 0 1110 0010<br />

nach 5. Taktflanke 1 0001 0010<br />

nach 6. Taktflanke 0 1111 0100<br />

nach 7. Taktflanke 0 0010 0100<br />

Frage 5 a) In welchem Register steht nach erfolgter Division der Quotient?<br />

(6 Punkte)<br />

Im Register MQ.<br />

b) In welchem Register steht nach erfolgter Division der Rest?<br />

Im Register AC.<br />

c) Beschreiben Sie den verwendeten Divisionsalgorithmus in eigenen Worten.<br />

Akkumulator <strong>und</strong> MQ werden nach links geschoben, dann von der oberen Hälfte<br />

des geschobenen Doppelwortes MD subtrahiert. Ist das Ergebnis positiv<br />

(c = ’0’), so wird als Quotientenstelle ’1’ in MQ eingeschoben. Ist das Ergebnis<br />

negativ (c = ’1’), so wird als Quotientenstelle ’0’ in MQ eingeschoben, <strong>und</strong> in<br />

einem darauffolgenden Korrekturschritt wird MD wieder zu AC addiert.<br />

Aufgabe 2 Seite 5

Frage 6<br />

(9 Punkte)<br />

Zeichnen Sie ein geeignetes Zustands-Übergangsdiagramm, das das Verhalten<br />

des Automaten vollständig (einschließlich Ein- <strong>und</strong> Ausgangssignale)<br />

beschreibt.<br />

s0<br />

1<br />

1<br />

k0<br />

0<br />

0<br />

s1<br />

1<br />

1<br />

k1<br />

0<br />

0<br />

s2<br />

1<br />

1<br />

k2<br />

0<br />

0<br />

s3<br />

1<br />

1<br />

k3<br />

0<br />

0<br />

dead<br />

0<br />

Aufgabe 2 Seite 6

Frage 7 a) Geben Sie die Deklaration eines Typs zur Beschreibung des Zustands des<br />

Automaten an.<br />

(20 Punkte)<br />

type state_type is (s0, s1, s2, s3, k0, k1, k2, k3, dead);<br />

b) Geben Sie die Deklaration je eines Signals <strong>für</strong> den Istzustand<br />

current_state <strong>und</strong> den Folgezustand next_state an.<br />

signal current_state, next_state: state_type;<br />

c) Geben Sie einen Prozess zur Ermittlung des Folgezustandes an.<br />

process(current_state, c) is<br />

begin<br />

case current_state is<br />

when s0 =><br />

if c = ’1’ then next_state

Teil 3<br />

Frage 8<br />

(16 Punkte)<br />

Verhaltensbeschreibung <strong>für</strong> das Dividierwerk<br />

Beschreiben Sie das Verhalten des Dividierwerks gemäß Bild 1 (d.h. ohne<br />

Steuerung) in Form einer reinen Verhaltensbeschreibung (Architecture behav),<br />

die neben Signaldeklarationen nur zwei Prozesse <strong>und</strong> eine nebenläufige<br />

Signalzuweisung enthält.<br />

library ieee; use ieee.numeric_std.all;<br />

architecture behav of mult is<br />

signal md, mq, ac: std_logic_vector(N-1 downto 0);<br />

signal aux: unsigned(N downto 0);<br />

begin<br />

process(mode, ac, mq, md) is<br />

begin<br />

if mode = ’1’ then<br />

aux