Gecko3 - CCC Event Weblog

Gecko3 - CCC Event Weblog

Gecko3 - CCC Event Weblog

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

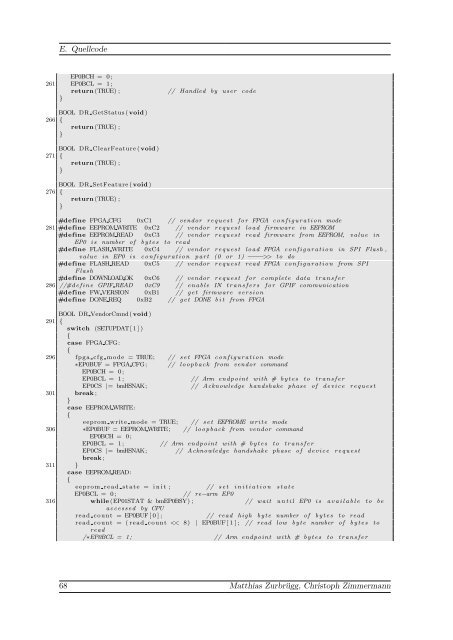

E. Quellcode<br />

EP0BCH = 0 ;<br />

261 EP0BCL = 1 ;<br />

return (TRUE) ; // Handled by user code<br />

}<br />

BOOL DR GetStatus ( void )<br />

266 {<br />

return (TRUE) ;<br />

}<br />

BOOL DR ClearFeature ( void )<br />

271 {<br />

return (TRUE) ;<br />

}<br />

BOOL DR SetFeature ( void )<br />

276 {<br />

return (TRUE) ;<br />

}<br />

#define FPGA CFG 0xC1 // vendor r e q u e s t f o r FPGA c o n f i g u r a t i o n mode<br />

281 #define EEPROM WRITE 0xC2 // vendor r e q u e s t l o a d firmware in EEPROM<br />

#define EEPROM READ 0xC3 // vendor r e q u e s t read firmware from EEPROM, v a l u e in<br />

EP0 i s number o f b y t e s to read<br />

#define FLASH WRITE 0xC4 // vendor r e q u e s t l o a d FPGA c o n f i g u r a t i o n in SPI Flash ,<br />

v a l u e in EP0 i s c o n f i g u r a t i o n p a r t (0 or 1) −−−−>> to do<br />

#define FLASH READ 0xC5 // vendor r e q u e s t read FPGA c o n f i g u r a t i o n from SPI<br />

Flash<br />

#define DOWNLOADOK 0xC6 // vendor r e q u e s t f o r complete data t r a n s f e r<br />

286 //#d e f i n e GPIF READ 0xC9 // e n a b l e IN t r a n s f e r s f o r GPIF communication<br />

#define FW VERSION 0xB1 // g e t firmware v e r s i o n<br />

#define DONE REQ 0xB2 // g e t DONE b i t from FPGA<br />

BOOL DR VendorCmnd( void )<br />

291 {<br />

switch (SETUPDAT[ 1 ] )<br />

{<br />

case FPGA CFG:<br />

{<br />

296 fpga cfg m ode = TRUE; // s e t FPGA c o n f i g u r a t i o n mode<br />

∗EP0BUF = FPGA CFG; // l o o p b a c k from vendor command<br />

EP0BCH = 0 ;<br />

EP0BCL = 1 ; // Arm endpoint with # b y t e s to t r a n s f e r<br />

EP0CS |= bmHSNAK; // Acknowledge handshake phase o f d e v i c e r e q u e s t<br />

301 break ;<br />

}<br />

case EEPROM WRITE:<br />

{<br />

eeprom write mode = TRUE; // s e t EEPROME w r i t e mode<br />

306 ∗EP0BUF = EEPROM WRITE; // l o o p b a c k from vendor command<br />

EP0BCH = 0 ;<br />

EP0BCL = 1 ; // Arm endpoint with # b y t e s to t r a n s f e r<br />

EP0CS |= bmHSNAK; // Acknowledge handshake phase o f d e v i c e r e q u e s t<br />

break ;<br />

311 }<br />

case EEPROM READ:<br />

{<br />

e e p r o m r e a d s t a t e = i n i t ; // s e t i n i t i a t i o n s t a t e<br />

EP0BCL = 0 ; // re−arm EP0<br />

316 while (EP01STAT & bmEP0BSY) ; // wait u n t i l EP0 i s a v a i l a b l e to be<br />

a c c e s s e d by CPU<br />

r e a d c o u n t = EP0BUF [ 0 ] ; // read high b y t e number o f b y t e s to read<br />

r e a d c o u n t = ( r e a d c o u n t