Gecko3 - CCC Event Weblog

Gecko3 - CCC Event Weblog

Gecko3 - CCC Event Weblog

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

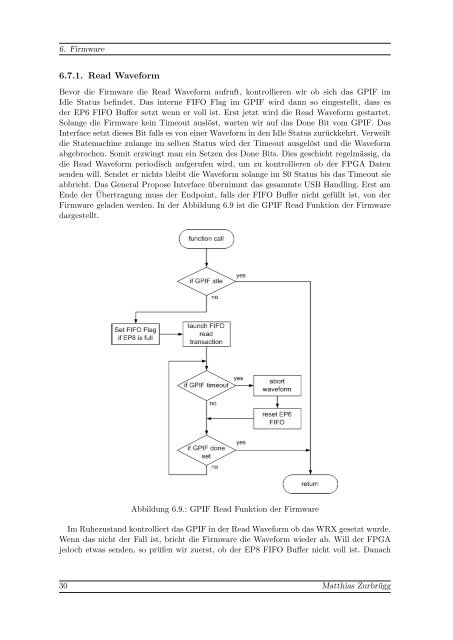

6. Firmware<br />

6.7.1. Read Waveform<br />

Bevor die Firmware die Read Waveform aufruft, kontrollieren wir ob sich das GPIF im<br />

Idle Status befindet. Das interne FIFO Flag im GPIF wird dann so eingestellt, dass es<br />

der EP6 FIFO Buffer setzt wenn er voll ist. Erst jetzt wird die Read Waveform gestartet.<br />

Solange die Firmware kein Timeout auslöst, warten wir auf das Done Bit vom GPIF. Das<br />

Interface setzt dieses Bit falls es von einer Waveform in den Idle Status zurückkehrt. Verweilt<br />

die Statemachine zulange im selben Status wird der Timeout ausgelöst und die Waveform<br />

abgebrochen. Somit erzwingt man ein Setzen des Done Bits. Dies geschieht regelmässig, da<br />

die Read Waveform periodisch aufgerufen wird, um zu kontrollieren ob der FPGA Daten<br />

senden will. Sendet er nichts bleibt die Waveform solange im S0 Status bis das Timeout sie<br />

abbricht. Das General Propose Interface übernimmt das gesammte USB Handling. Erst am<br />

Ende der Übertragung muss der Endpoint, falls der FIFO Buffer nicht gefüllt ist, von der<br />

Firmware geladen werden. In der Abbildung 6.9 ist die GPIF Read Funktion der Firmware<br />

dargestellt.<br />

Abbildung 6.9.: GPIF Read Funktion der Firmware<br />

Im Ruhezustand kontrolliert das GPIF in der Read Waveform ob das WRX gesetzt wurde.<br />

Wenn das nicht der Fall ist, bricht die Firmware die Waveform wieder ab. Will der FPGA<br />

jedoch etwas senden, so prüfen wir zuerst, ob der EP8 FIFO Buffer nicht voll ist. Danach<br />

30 Matthias Zurbrügg