Antriebssystem für höchste Geschwindigkeiten - Bergische ...

Antriebssystem für höchste Geschwindigkeiten - Bergische ...

Antriebssystem für höchste Geschwindigkeiten - Bergische ...

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

4. Signalgewinnung und Signalaufbereitung 50<br />

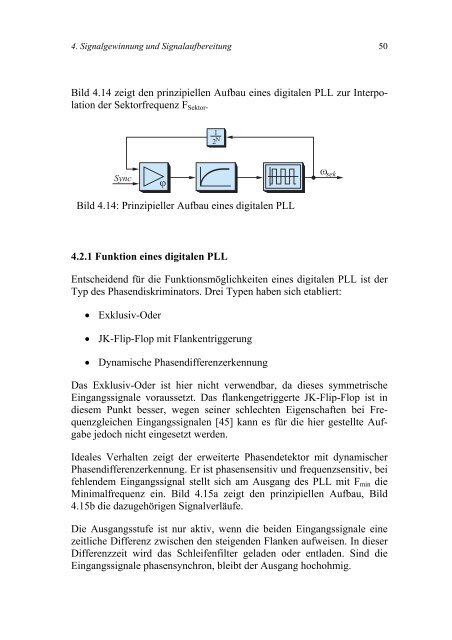

Bild 4.14 zeigt den prinzipiellen Aufbau eines digitalen PLL zur Interpolation<br />

der Sektorfrequenz FSektor.<br />

Sync<br />

�<br />

Bild 4.14: Prinzipieller Aufbau eines digitalen PLL<br />

1<br />

2 N<br />

4.2.1 Funktion eines digitalen PLL<br />

� sek<br />

Entscheidend <strong>für</strong> die Funktionsmöglichkeiten eines digitalen PLL ist der<br />

Typ des Phasendiskriminators. Drei Typen haben sich etabliert:<br />

• Exklusiv-Oder<br />

• JK-Flip-Flop mit Flankentriggerung<br />

• Dynamische Phasendifferenzerkennung<br />

Das Exklusiv-Oder ist hier nicht verwendbar, da dieses symmetrische<br />

Eingangssignale voraussetzt. Das flankengetriggerte JK-Flip-Flop ist in<br />

diesem Punkt besser, wegen seiner schlechten Eigenschaften bei Frequenzgleichen<br />

Eingangssignalen [45] kann es <strong>für</strong> die hier gestellte Aufgabe<br />

jedoch nicht eingesetzt werden.<br />

Ideales Verhalten zeigt der erweiterte Phasendetektor mit dynamischer<br />

Phasendifferenzerkennung. Er ist phasensensitiv und frequenzsensitiv, bei<br />

fehlendem Eingangssignal stellt sich am Ausgang des PLL mit Fmin die<br />

Minimalfrequenz ein. Bild 4.15a zeigt den prinzipiellen Aufbau, Bild<br />

4.15b die dazugehörigen Signalverläufe.<br />

Die Ausgangsstufe ist nur aktiv, wenn die beiden Eingangssignale eine<br />

zeitliche Differenz zwischen den steigenden Flanken aufweisen. In dieser<br />

Differenzzeit wird das Schleifenfilter geladen oder entladen. Sind die<br />

Eingangssignale phasensynchron, bleibt der Ausgang hochohmig.