VHDL Kompakt - CES

VHDL Kompakt - CES

VHDL Kompakt - CES

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

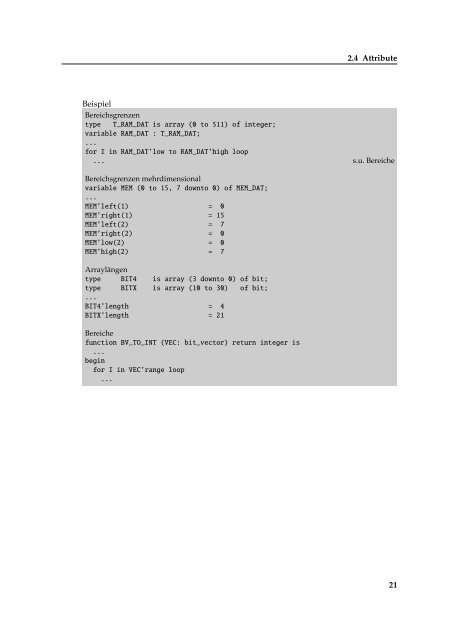

2.4 Attribute<br />

Beispiel<br />

Bereichsgrenzen<br />

type T_RAM_DAT is array (0 to 511) of integer;<br />

variable RAM_DAT : T_RAM_DAT;<br />

...<br />

for I in RAM_DAT’low to RAM_DAT’high loop<br />

... s.u. Bereiche<br />

Bereichsgrenzen mehrdimensional<br />

variable MEM (0 to 15, 7 downto 0) of MEM_DAT;<br />

...<br />

MEM’left(1) = 0<br />

MEM’right(1) = 15<br />

MEM’left(2) = 7<br />

MEM’right(2) = 0<br />

MEM’low(2) = 0<br />

MEM’high(2) = 7<br />

Arraylängen<br />

type BIT4 is array (3 downto 0) of bit;<br />

type BITX is array (10 to 30) of bit;<br />

...<br />

BIT4’length = 4<br />

BITX’length = 21<br />

Bereiche<br />

function BV_TO_INT (VEC: bit_vector) return integer is<br />

...<br />

begin<br />

for I in VEC’range loop<br />

...<br />

21