1.8 Grundlagen der Digitaltechnik

1.8 Grundlagen der Digitaltechnik

1.8 Grundlagen der Digitaltechnik

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Informatik V, Kap. 8, WS 98/99<br />

8.5.9 Dynamische CMOS-Logik<br />

Die gegenüber nMOS hohe Zahl <strong>der</strong> Transistoren in statischen CMOS-Schaltungen war <strong>der</strong> Anlaß,<br />

nach alternativen Schaltungstechniken zu suchen.<br />

Zunächst ist es natürlich möglich, in CMOS eine Quasi- nMOS-Schaltungstechnik zu bauen. Dazu<br />

wird man typischerweise einen selbstleitend geschalteten p-Kanal-Transistor als "pull-up-Transistor"<br />

verwenden.<br />

VDD<br />

Eingänge<br />

n-Kanal -<br />

Netzwerk<br />

GND<br />

Abb. 8.53: Quasi-nMOS-Gatter<br />

Ausgang<br />

Diese Schaltung bietet wie<strong>der</strong>um alle negativen Eigenschaften <strong>der</strong> nMOS-Schaltungstechnik und hat<br />

sich deshalb nicht durchgesetzt.<br />

f1<br />

f1<br />

Eingänge<br />

VDD<br />

n-Kanal -<br />

Netzwerk<br />

GND<br />

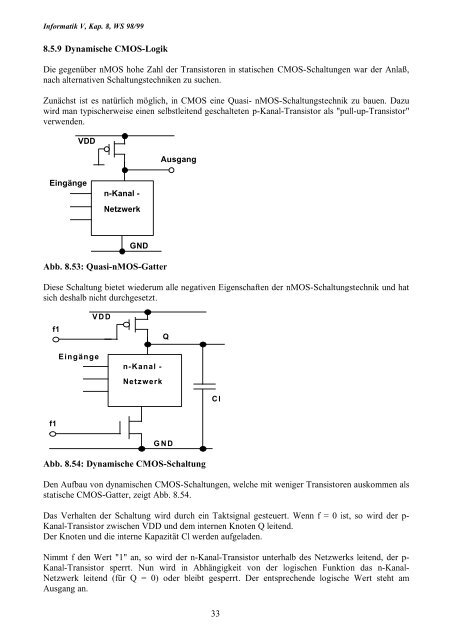

Abb. 8.54: Dynamische CMOS-Schaltung<br />

Q<br />

Cl<br />

Den Aufbau von dynamischen CMOS-Schaltungen, welche mit weniger Transistoren auskommen als<br />

statische CMOS-Gatter, zeigt Abb. 8.54.<br />

Das Verhalten <strong>der</strong> Schaltung wird durch ein Taktsignal gesteuert. Wenn f = 0 ist, so wird <strong>der</strong> p-<br />

Kanal-Transistor zwischen VDD und dem internen Knoten Q leitend.<br />

Der Knoten und die interne Kapazität Cl werden aufgeladen.<br />

Nimmt f den Wert "1" an, so wird <strong>der</strong> n-Kanal-Transistor unterhalb des Netzwerks leitend, <strong>der</strong> p-<br />

Kanal-Transistor sperrt. Nun wird in Abhängigkeit von <strong>der</strong> logischen Funktion das n-Kanal-<br />

Netzwerk leitend (für Q = 0) o<strong>der</strong> bleibt gesperrt. Der entsprechende logische Wert steht am<br />

Ausgang an.<br />

33