Grundlagen der Technischen Informatik

Grundlagen der Technischen Informatik Grundlagen der Technischen Informatik

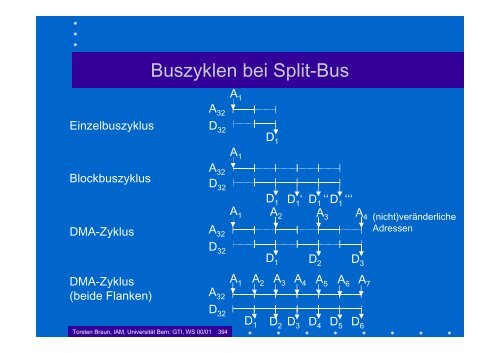

Einzelbuszyklus Blockbuszyklus DMA-Zyklus DMA-Zyklus (beide Flanken) Torsten Braun, IAM, Universität Bern: GTI, WS 00/01 394 Buszyklen bei Split-Bus A 32 D 32 A 32 D 32 A 32 D 32 A 32 D 32 A 1 A 1 D 1 D 1 D1 ‘ D1 ‘‘D1 ‘‘‘ A1 A2 A3 A4 A 1 A 2 A 3 A 4 D 1 D 1 D 3 D 2 A 5 A 6 A 7 D 2 D 4 D 6 D 5 D 3 (nicht)veränderliche Adressen

langer Blockbuszyklus langer Blockbuszyklus (beide Flanken) Buszyklen bei Multiplex-Bus Einzelbuszyklus AD64 AD64 D1 D1 Lesen Schreiben Blockbuszyklus AD 64 AD 64 AD 64 Torsten Braun, IAM, Universität Bern: GTI, WS 00/01 395 A 1 A 1 A 1 A 1 D Turnaround- Zyklus D 1 A 1 D 1 ‘ D 1 ‘‘D 1 ‘‘‘ D D D D D D D D D D D D D D D D D Schreiben

- Seite 3 und 4: Input Next-State- Logik Torsten Bra

- Seite 5 und 6: Komponenten eines Mikrorechnersyste

- Seite 7 und 8: Struktur eines von-Neumann-Rechners

- Seite 9 und 10: Kennzeichen eines von-Neumann-Rechn

- Seite 11 und 12: Torsten Braun, IAM, Universität Be

- Seite 13 und 14: Torsten Braun, IAM, Universität Be

- Seite 15 und 16: Torsten Braun, IAM, Universität Be

- Seite 17 und 18: (Maschinen-)Befehlszyklus • Ablau

- Seite 19 und 20: Torsten Braun, IAM, Universität Be

- Seite 21 und 22: Torsten Braun, IAM, Universität Be

- Seite 23 und 24: • Program Counter, PC Torsten Bra

- Seite 25 und 26: Torsten Braun, IAM, Universität Be

- Seite 27 und 28: CWP -1 +1 3 4 1 +1 Datenregisterspe

- Seite 29 und 30: Programm- und Datenspeicher mit Zug

- Seite 31 und 32: Datenspeicher für aktuellen Datena

- Seite 33 und 34: Arithmetisch-logische Operationen i

- Seite 35 und 36: instruction fetch instruction decod

- Seite 37 und 38: Very Long Instruction Word (VLIW)

- Seite 39 und 40: Torsten Braun, IAM, Universität Be

- Seite 41 und 42: Unstrukturierte Registerspeicher

- Seite 43 und 44: Registerfenster variabler Grösse

- Seite 45 und 46: Torsten Braun, IAM, Universität Be

- Seite 47 und 48: Torsten Braun, IAM, Universität Be

- Seite 49 und 50: Sammelleitungen Stichleitungen Dais

- Seite 51 und 52: Torsten Braun, IAM, Universität Be

- Seite 53: • Einzelbuszyklus Torsten Braun,

- Seite 57 und 58: Torsten Braun, IAM, Universität Be

- Seite 59 und 60: m D m m D: Datenleitungen m +1 Tors

- Seite 61 und 62: ROM und RAM-Speicher • Read Only

- Seite 63 und 64: Steuerlogik Torsten Braun, IAM, Uni

- Seite 65 und 66: Content Addressable Memory (CAM) Al

- Seite 67 und 68: • Ebenen Adressierungshierarchie

- Seite 69 und 70: Byte-, Halbwort-, Wortanwahl • By

- Seite 71 und 72: Prozessorregister 3 2 1 0 Datenbus

- Seite 73 und 74: BUSCLK CSTART (Master) READY (Slave

- Seite 75 und 76: CPUCLK AS DS DTACK Torsten Braun, I

- Seite 77 und 78: Master Slave Prozessortakt A31-2,BE

- Seite 79 und 80: Takt A31-4 BE3-0 A3-2 R/W CSTART LA

- Seite 81 und 82: CS WE A9-A0 D in Schreibverstärker

- Seite 83 und 84: WE CAS RAS A10-A0/ A21-11 Refresh-

- Seite 85 und 86: Adresse RAS CAS WE D in D out Schre

- Seite 87 und 88: 0 4 4M-4 4M 8M-4 Aufbau von Speiche

- Seite 89 und 90: DRAM-Controller READY Steuerung Ver

- Seite 91 und 92: Torsten Braun, IAM, Universität Be

- Seite 93 und 94: • I/O-Unit • Schnittstelle zwis

- Seite 95 und 96: Steuerung der Ein-/Ausgabe • Anfo

- Seite 97: Ausblick: Rechnerarchitektur • Vo

Einzelbuszyklus<br />

Blockbuszyklus<br />

DMA-Zyklus<br />

DMA-Zyklus<br />

(beide Flanken)<br />

Torsten Braun, IAM, Universität Bern: GTI, WS 00/01 394<br />

Buszyklen bei Split-Bus<br />

A 32<br />

D 32<br />

A 32<br />

D 32<br />

A 32<br />

D 32<br />

A 32<br />

D 32<br />

A 1<br />

A 1<br />

D 1<br />

D 1<br />

D1 ‘ D1 ‘‘D1 ‘‘‘<br />

A1 A2 A3 A4 A 1 A 2 A 3 A 4<br />

D 1<br />

D 1<br />

D 3<br />

D 2<br />

A 5 A 6 A 7<br />

D 2 D 4 D 6<br />

D 5<br />

D 3<br />

(nicht)verän<strong>der</strong>liche<br />

Adressen