Grundlagen der Technischen Informatik

Grundlagen der Technischen Informatik Grundlagen der Technischen Informatik

μIR +1 Registerspeicher μPC CISC-Prozessorstruktur Mikroprogrammspeicher μCS 4 4 DR1 DR2 SR DB1 CC ALU 6 4 DB2 5 Torsten Braun, IAM, Universität Bern: GTI, WS 00/01 352 5 5 2 PC Befehlsdekodierung: Verzweigung im Mikroprogramm 1,3 4 IR AR 1,3 +1 1 3 1,3,4 1,3,4 Hauptspeicher C A D

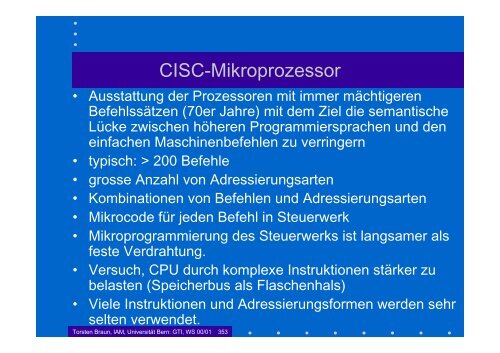

Torsten Braun, IAM, Universität Bern: GTI, WS 00/01 353 CISC-Mikroprozessor • Ausstattung der Prozessoren mit immer mächtigeren Befehlssätzen (70er Jahre) mit dem Ziel die semantische Lücke zwischen höheren Programmiersprachen und den einfachen Maschinenbefehlen zu verringern • typisch: > 200 Befehle • grosse Anzahl von Adressierungsarten • Kombinationen von Befehlen und Adressierungsarten • Mikrocode für jeden Befehl in Steuerwerk • Mikroprogrammierung des Steuerwerks ist langsamer als feste Verdrahtung. • Versuch, CPU durch komplexe Instruktionen stärker zu belasten (Speicherbus als Flaschenhals) • Viele Instruktionen und Adressierungsformen werden sehr selten verwendet.

- Seite 1 und 2: Grundlagen der Technischen Informat

- Seite 3 und 4: Input Next-State- Logik Torsten Bra

- Seite 5 und 6: Komponenten eines Mikrorechnersyste

- Seite 7 und 8: Struktur eines von-Neumann-Rechners

- Seite 9 und 10: Kennzeichen eines von-Neumann-Rechn

- Seite 11: Torsten Braun, IAM, Universität Be

- Seite 15 und 16: Torsten Braun, IAM, Universität Be

- Seite 17 und 18: (Maschinen-)Befehlszyklus • Ablau

- Seite 19 und 20: Torsten Braun, IAM, Universität Be

- Seite 21 und 22: Torsten Braun, IAM, Universität Be

- Seite 23 und 24: • Program Counter, PC Torsten Bra

- Seite 25 und 26: Torsten Braun, IAM, Universität Be

- Seite 27 und 28: CWP -1 +1 3 4 1 +1 Datenregisterspe

- Seite 29 und 30: Programm- und Datenspeicher mit Zug

- Seite 31 und 32: Datenspeicher für aktuellen Datena

- Seite 33 und 34: Arithmetisch-logische Operationen i

- Seite 35 und 36: instruction fetch instruction decod

- Seite 37 und 38: Very Long Instruction Word (VLIW)

- Seite 39 und 40: Torsten Braun, IAM, Universität Be

- Seite 41 und 42: Unstrukturierte Registerspeicher

- Seite 43 und 44: Registerfenster variabler Grösse

- Seite 45 und 46: Torsten Braun, IAM, Universität Be

- Seite 47 und 48: Torsten Braun, IAM, Universität Be

- Seite 49 und 50: Sammelleitungen Stichleitungen Dais

- Seite 51 und 52: Torsten Braun, IAM, Universität Be

- Seite 53 und 54: • Einzelbuszyklus Torsten Braun,

- Seite 55 und 56: langer Blockbuszyklus langer Blockb

- Seite 57 und 58: Torsten Braun, IAM, Universität Be

- Seite 59 und 60: m D m m D: Datenleitungen m +1 Tors

- Seite 61 und 62: ROM und RAM-Speicher • Read Only

Torsten Braun, IAM, Universität Bern: GTI, WS 00/01 353<br />

CISC-Mikroprozessor<br />

• Ausstattung <strong>der</strong> Prozessoren mit immer mächtigeren<br />

Befehlssätzen (70er Jahre) mit dem Ziel die semantische<br />

Lücke zwischen höheren Programmiersprachen und den<br />

einfachen Maschinenbefehlen zu verringern<br />

• typisch: > 200 Befehle<br />

• grosse Anzahl von Adressierungsarten<br />

• Kombinationen von Befehlen und Adressierungsarten<br />

• Mikrocode für jeden Befehl in Steuerwerk<br />

• Mikroprogrammierung des Steuerwerks ist langsamer als<br />

feste Verdrahtung.<br />

• Versuch, CPU durch komplexe Instruktionen stärker zu<br />

belasten (Speicherbus als Flaschenhals)<br />

• Viele Instruktionen und Adressierungsformen werden sehr<br />

selten verwendet.